**Nonlinear Modeling of GaAs pHEMTs**

for Millimeter-Wave Mixer Design

Giovanni Crupi<sup>1\*</sup>, Antonio Raffo<sup>2</sup>, Gustavo Avolio<sup>3</sup>, Gianni Bosi<sup>2</sup>, Giuseppe Sivverini<sup>4</sup>,

Francesco Palomba<sup>4</sup>, Alina Caddemi<sup>1</sup>, Dominique M. M.-P. Schreurs<sup>3</sup>, and Giorgio Vannini<sup>2</sup>

1

<sup>1</sup>DICIEAMA, University of Messina, 98166 Messina, Italy

\*Phone: +39-0903977327, fax: +39-0903977571, e-mail: crupig@unime.it

<sup>2</sup>Department of Engineering, University of Ferrara, 44122 Ferrara, Italy

<sup>3</sup>Electronic Engineering Department, KU Leuven, B-3001 Leuven, Belgium

<sup>4</sup>TriQuint Semiconductor, Dallas, 75080 Texas, USA

Abstract—The present paper is focused on the extraction of a GaAs pHEMT nonlinear model meant for

mixer design. The model is based on an equivalent circuit that is analytically extracted from DC and

multi-bias and -frequency S-parameter measurements and then implemented in a nonlinear RF circuit

simulator by using look-up tables. The model accuracy is extensively verified by comparing device

measurements and simulations under a wide range of operating conditions. Furthermore, to corroborate

the validity of the model, the design of a Q-band up-converter is considered.

**Keywords:** design; equivalent circuit; microwave measurements; mixer; modeling; pHEMTs.

1. Introduction

High-frequency equivalent circuit modeling of active solid-state devices is a very attractive field of ongoing research because of its crucial role for a fast and reliable development of both device fabrication and circuit design processes. Nowadays, there is considerable and growing interest in the determination of nonlinear models able to reproduce the device behavior under realistic RF operating conditions [1][3]. This is due to the increasing number of telecommunication applications that need the device to operate in a highly nonlinear regime, such as power amplifiers and mixers [4]-[8].

In this context, the purpose of this paper is to analytically extract and fully validate a nonlinear high-frequency model for GaAs pseudomorphic high electron mobility transistors (pHEMTs) for cold-FET mixer design. As well known, the core of the device model is its intrinsic section representing the actual nonlinear transistor. To implement the model in a commercial circuit simulator, the nonlinear intrinsic section can be represented by analytical functions [9]-[16] and/or look-up tables [17]-[25]. In the present case, the lookup table approach is adopted because of its key advantage of being a straightforward representation without requiring complex model functions, which can be very challenging and time consuming to construct and fit. It is worth noting that the determination of the model at negative  $V_{DS}$  is a critical step for mixer applications [26]-[30]. In light of that, the present model accounts for potential asymmetries as the model extraction is performed also at negative  $V_{DS}$  without the need of assuming a symmetric behavior of the device. Furthermore, the standard formulae for determining the transconductance and its delay at positive  $V_{DS}$  are modified for their extraction at negative  $V_{DS}$ . Specifically, the sign of  $g_m$  is changed at negative  $V_{DS}$  and such a  $\pi$  phase shift is subtracted before evaluating  $\tau$ .

The paper is organized into five parts. Section 2 is dedicated to presenting the advanced tested pHEMTs fabricated in GaAs technology with a gate length of 0.15  $\mu$ m. The two investigated devices have different gate width: 200  $\mu$ m and 300  $\mu$ m. Section 3 is aimed at describing the procedure for determining and implementing the equivalent circuit model, while Section 4 is devoted to its validation based on the comparison between measurements and simulations. Subsequently, Section 5 shows the comparison between measured and simulated performance of a Q-band up-converter designed and realized by using the 0.15 x 300  $\mu$ m<sup>2</sup> transistor modeled in the present study. The Q-band ranges from

33 to 50 GHz and is widely used for several applications in satellite and terrestrial microwave communications and radio astronomy. Finally, conclusive remarks are given in Section 6.

### 2. Device characterization

The two studied transistors are on-wafer GaAs pHEMTs fabricated by TriQuint Semiconductor [31]. The two devices have a gate length of 0.15  $\mu$ m and a gate width of 200  $\mu$ m and 300  $\mu$ m, respectively. To improve their microwave performance, the layouts of the two devices are based on four interdigitated fingers with lengths of 50  $\mu$ m and 75  $\mu$ m, respectively. Furthermore, to minimize discontinuities between the transmission lines and the actual transistor, tapers are used at both gate-source and drain-source ports.

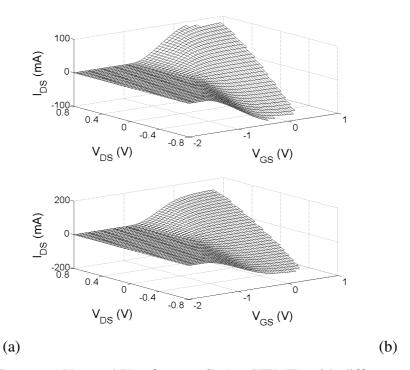

Device characterization is based on multi-bias scattering (S-) parameters measured from 2.5 GHz to 65 GHz. To put in evidence the wide range of bias points used for S-parameter measurements, Fig. 1 reports the corresponding measured values of I<sub>D</sub> versus V<sub>GS</sub> and V<sub>DS</sub>. It should be highlighted that a small step of 50 mV has been used for both gate and drain voltages to guarantee good interpolation properties of the intrinsic look-up table model. This is because the intrinsic multi-bias small-signal equivalent circuit obtained from S-parameter measurements is used to build the nonlinear model, which is implemented by means of a symbolically defined device (SDD) component available in Agilent's advanced design system (ADS) circuit simulator [32]. Furthermore, it should be underlined that, based on the presented modeling technique, the model parameters are calculated from the measurements with appropriate scripts developed in MATLAB software. The S-parameter measurements on the device are achieved by using a TRL on-wafer calibration followed by matrix manipulations to remove the contributions of the input and output tapers. In particular, the shift of the reference planes is obtained by using the following formula based on the transmission (T-) parameters, known also as the chain parameters, as they are very helpful when working with networks connected in cascade [33]:

$$[T_{\text{DUT}}] = [T_{\text{INPUT\_TAPER}}]^{-1} [T_{\text{DUT+TAPERS}}] [T_{\text{OUTPUT\_TAPER}}]^{-1}$$

$$(1)$$

where the behavior of the tapers is accurately determined by electromagnetic simulations.

Hence, the extrinsic effects arising from the tapers are disregarded in the present model since the model extraction is based on the S-parameter measurements after de-embedding the taper contributions. On the other hand, off-wafer calibrations are used for the nonlinear measurements devoted to the model validation at both low and high frequencies. This implies that the calibration reference planes have been set at the probe tips. The contributions associated to the path from the probe tips to the taper ends have to be considered at microwave frequencies; therefore they are properly modelled by using electromagnetic simulations. On the contrary, these access structures can be totally neglected at low frequencies (i.e., in the megahertz range) since they produce inductive and capacitive effects that are of the order of 100 pH and 50 fF respectively, whereas their resistive losses are below 50 m $\Omega$ .

**Fig. 1.** Behavior of  $I_D$  versus  $V_{DS}$  and  $V_{GS}$  for two GaAs pHEMTs with different gate widths: 200  $\mu$ m (a) and 300  $\mu$ m (b).

## 3. Equivalent circuit extraction

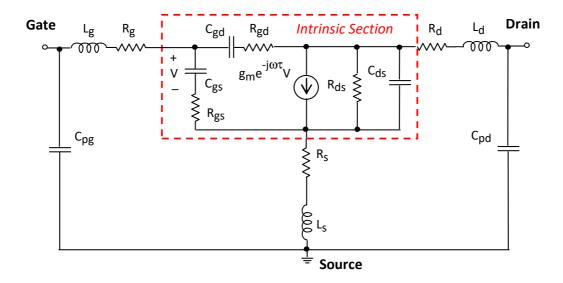

Fig. 2 shows the small-signal equivalent circuit used for the tested GaAs pHEMTs. This circuit can be divided into two main sections: the extrinsic part, whose elements are assumed to be bias-independent, and the intrinsic section, whose elements are bias dependent. The values of the circuit elements are determined from S-parameter measurements. In particular, the extrinsic elements are firstly extracted from "cold" S-parameters (i.e.,  $V_{DS} = 0$  V) [34]-[40]. Successively, de-embedding of the extrinsic elements from the measurements is carried out with simple matrix manipulations, and the intrinsic elements are calculated from the intrinsic admittance (Y-) parameters at each investigated bias point by using well known formulae [33]. It should be highlighted that the transconductance and its delay are obtained at negative  $V_{DS}$  by modifying the standard formulae used for positive  $V_{DS}$ . In particular, at negative  $V_{DS}$  the sign of  $g_m$  must be changed and this  $\pi$  phase shift has to be subtracted before calculating  $\tau$ :

$$G = g_{m}e^{-j\omega\tau} = (Y_{2I} - Y_{I2})\left[1 + j\frac{\operatorname{Re}(Y_{II} + Y_{I2})}{\operatorname{Im}(Y_{II} + Y_{I2})}\right] \begin{cases} for \ V_{DS} > 0 \end{cases} \begin{cases} g_{m} = |G| \\ \tau = -\frac{1}{\omega}\angle G \end{cases}$$

$$for \ V_{DS} < 0 \end{cases} \begin{cases} g_{m} = -|G| \\ \tau = -\frac{1}{\omega}(\angle G - \pi) \end{cases}$$

(2)

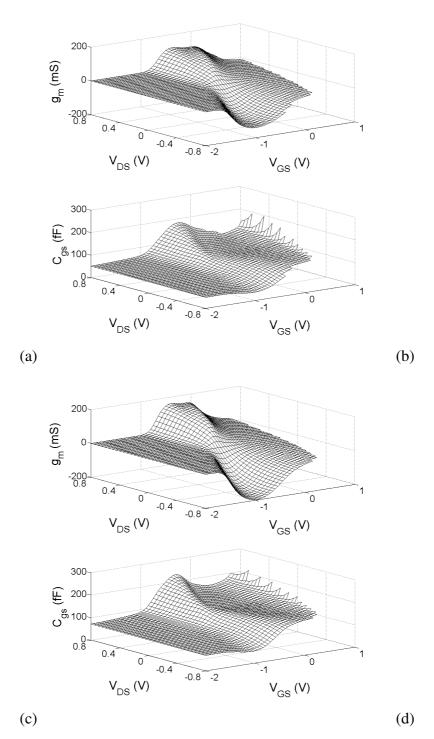

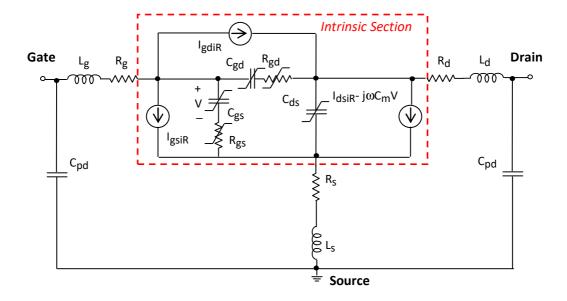

The bias dependences of the intrinsic  $g_m$  and  $C_{gs}$  for the two tested devices are illustrated in Fig. 3. Subsequently, the achieved multi-bias small-signal equivalent circuit is used as the starting point to build the large-signal model shown in Fig. 4. As can be seen, the transconductance delay  $\tau$  is approximated with the transcapacitance (i.e.,  $C_m = g_m \tau$ ) by using only the first term in the Taylor series expansion for the function  $e^{-j\omega\tau}$  (i.e.,  $e^{-j\omega\tau} = g_m - j\omega C_m$ ) [41], [42]. The conduction gate and drain currents are obtained from the measured DC values. Dedicated DC measurements at high values of the gate voltage are used to obtain the gate Schottky diode forward characteristics. The intrinsic circuit elements are stored in look-up tables versus the intrinsic voltages with the exception of the conduction

gate current that is modeled with an analytical function approach. This is because the better extrapolation capability of the analytical functions allows predicting more accurately the exponential current growth when the gate voltage is increased beyond the analyzed bias range. In particular, the standard diode model available in ADS has been adopted [32]. To model the forward conduction of the gate Schottky junction the ideality factor N and the inverse saturation current  $I_s$  have been identified by using the DC measurements performed at sufficiently high gate voltage, keeping the drain voltage constant to 0 V. After de-embedding these data from the resistive parasitic effects, we use them to identify the requested parameters through the optimization tool provided by ADS. To reproduce the reverse conduction, the breakdown voltage provided by the foundry has been considered.

It should be pointed out that low-frequency dispersion effects have not been included in the model [43]-[50], since the thermal phenomena can be disregarded under the low power-dissipation of mixer application and the trapping mechanisms are negligible for the studied GaAs pHEMTs which are based on a well-established technology.

**Fig. 2.** Small-signal equivalent circuit for GaAs pHEMT. The intrinsic section is highlighted by a dashed box.

**Fig. 3.** Behavior of  $g_m$  and  $C_{gs}$  versus  $V_{DS}$  and  $V_{GS}$  for two GaAs pHEMTs with different gate widths:  $200 \ \mu m$  (a, b) and  $300 \ \mu m$  (c, d).

**Fig. 4.** Large-signal equivalent circuit for GaAs pHEMT. The intrinsic section is highlighted by a dashed box.

# 4. Equivalent circuit validation

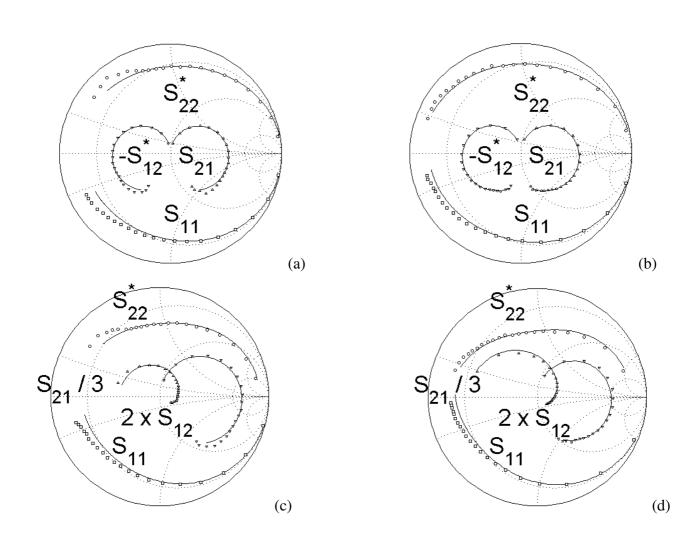

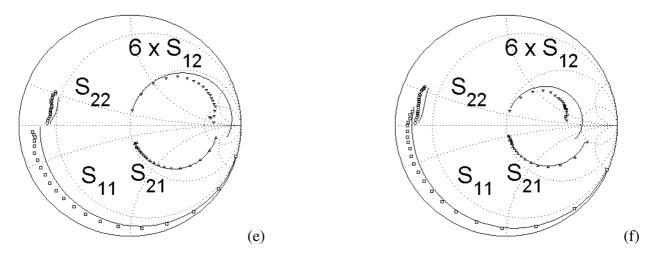

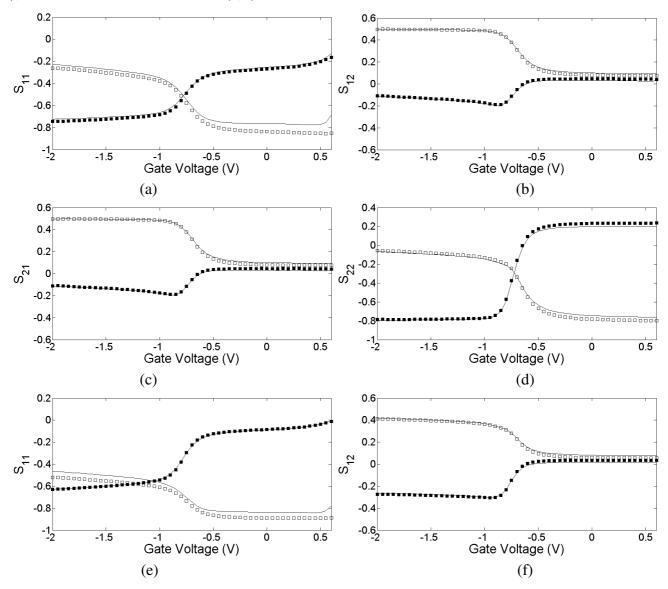

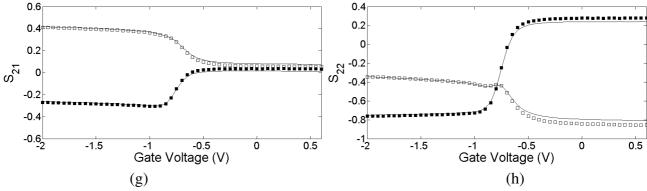

The obtained nonlinear model can reproduce accurately the measured S-parameters over the full investigated frequency range up to 65 GHz. As an illustrative example, Fig. 5 shows the good agreement between measured and simulated S-parameters for the tested devices at three different bias conditions:  $V_{DS} = 0$  V and  $V_{GS} = -1$  V,  $V_{DS} = 0.5$  V and  $V_{GS} = -0.8$  V,  $V_{DS} = -0.5$  V and  $V_{GS} = -0.5$  V. The model accuracy is confirmed by the low percentage errors  $E_{ij}$  between measured and simulated S-parameters (see Table I). The values of  $E_{ij}$  are achieved as follows:

$$E_{ij} = \frac{1}{N_f} \sum_{f} 100 \left| \frac{S_{ijMEASURED}(f) - S_{ijSIMULATED}(f)}{S_{ijMEASURED}(f)} \right|$$

(3)

where  $N_f$  is the frequency point number that is equal to 201 for the present study. It should be pointed out that the percentage error associated to  $S_{12}$  may reach very high values, due to its extremely small magnitude especially at low frequencies. Furthermore, Fig. 6 illustrates that the model can mimic very

well the behavior of the real and imaginary parts of the measured S-parameters versus  $V_{GS}$  with  $V_{DS} = 0$ V at the high frequency of 40 GHz.

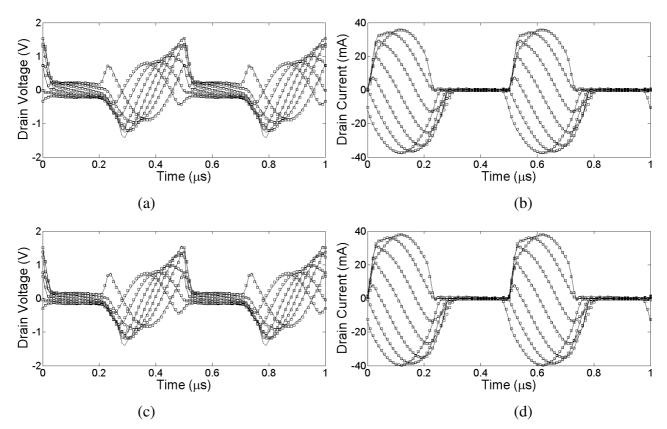

Fig. 7 presents the result of the nonlinear validation at low frequencies. In particular, it is shown that the model can accurately predict the measured drain voltage and current time-domain waveforms under cold-FET mixer application (i.e.,  $V_{DS} = 0 \text{ V}$  and  $V_{GS} = -1 \text{ V}$ ) with a fundamental frequency ( $f_0$ ) of 2 MHz for the tested GaAs pHEMTs. At such low frequency the nonlinear capacitive effects are negligible and then the achieved accuracy of the present model without a dedicated low-frequency dispersion network confirms that the impact of dispersive effects on the conduction drain current can be disregarded.

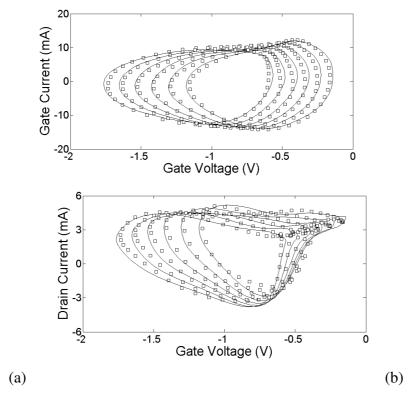

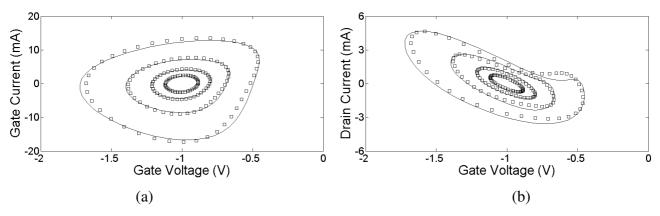

To validate the nonlinear model at high frequencies, the results of the simulations are compared with measurements performed by means of a large-signal network analyzer (LSNA) working up to 50 GHz. Fig. 8 reports the comparison between measured and simulated input and transfer loci for the device with a gate width of 300  $\mu$ m at  $f_0 = 10$  GHz,  $V_{DS} = 0$  V, and  $V_{GS}$  going from -1.1 V to -0.6 V with a step of 0.1 V. Fig. 9 illustrates the comparison between measured and simulated input and transfer loci for the device with a gate width of 200  $\mu$ m at 15 GHz,  $V_{DS} = 0$  V,  $V_{GS}$  -1 V, and for four different values of input power: -10.8 dBm, -5.8 dBm, -0.8 dBm, and 4.2 dBm. Furthermore, Fig. 10 shows measured and simulated output power and  $b_2/a_1$  phase versus input power for the device with a gate width of 300  $\mu$ m at  $V_{DS} = 0$  V,  $V_{GS} = -1$  V, and for two different values of the fundamental frequency: 38 GHz and 42 GHz.

The observed good agreement between model simulations and measurements under different operating conditions confirms the robustness of the extracted model.

**TABLE I.** The percentage errors between measured and simulated S-parameters for the two tested devices at three different bias conditions.

| Gate Width (µm) | $V_{DS}(V)$ | $V_{GS}(V)$ | E <sub>11</sub> (%) | E <sub>21</sub> (%) | E <sub>12</sub> (%) | E <sub>22</sub> (%) |

|-----------------|-------------|-------------|---------------------|---------------------|---------------------|---------------------|

| 200             | 0           | -1          | 4.4                 | 4.6                 | 4.6                 | 4.3                 |

| 300 | 0    | -1   | 3.6 | 3.4 | 3.4  | 4.1 |

|-----|------|------|-----|-----|------|-----|

| 200 | 0.5  | -0.8 | 4.8 | 6.3 | 4.2  | 4.7 |

| 300 | 0.5  | -0.8 | 4.4 | 8.2 | 3.2  | 5.6 |

| 200 | -0.5 | -0.5 | 5.2 | 5.6 | 22.2 | 7.3 |

| 300 | -0.5 | -0.5 | 3.7 | 9.9 | 32.6 | 6.2 |

**Fig. 5.** Comparison between measured (symbols) and simulated (lines) S-parameters from 2.5 GHz to 65 GHz for two GaAs pHEMTs with different gate widths: 200  $\mu$ m (a, c, e) and 300  $\mu$ m (b, d, f). The three analyzed bias conditions are:  $V_{DS} = 0$  V and  $V_{GS} = -1$  V (a, b),  $V_{DS} = 0.5$  V and  $V_{GS} = -0.8$  V (c, d),  $V_{DS} = -0.5$  V and  $V_{GS} = -0.5$  V (e, f).

**Fig. 6.** Comparison between measured (symbols) and simulated (lines) S-parameters versus  $V_{GS}$  from - 2 V to 0.6 V with 50 mV step at 40 GHz and  $V_{DS}$  = 0 V for two GaAs pHEMTs with different gate widths: 200  $\mu$ m (a, b, c, d) and 300  $\mu$ m (e, f, g, h). The real and imaginary parts of the measured S-parameters are, respectively, represented with white and black symbols.

**Fig. 7.** Comparison between measured (symbols) and simulated (lines) drain voltage and current time-domain waveforms at  $f_0 = 2$  MHz,  $V_{DS} = 0$  V, and  $V_{GS} = -1$  V for two GaAs pHEMTs with different gate widths: 200 μm (a, b) and 300 μm (c, d). The amplitude of the input and output incident waves and their relative phase are respectively:  $A_g = 1.5$  V,  $A_d = 1.5$  V, and  $\Delta \Phi = 0^\circ$ , 30°, 60°, 90°, 120°, 150°, 180°.

**Fig. 8.** Comparison between measured (symbols) and simulated (lines) input (a) and transfer (b) loci for a GaAs pHEMT with a gate width of 300  $\mu$ m at  $f_0 = 10$  GHz,  $V_{DS} = 0$  V, and  $V_{GS}$  from -1.1 V to -0.6 V with a step of 0.1 V.

**Fig. 9.** Comparison between measured (symbols) and simulated (lines) input (a) and transfer (b) loci for a GaAs pHEMT with a gate width of 200  $\mu$ m at  $f_0 = 15$  GHz,  $V_{DS} = 0$  V,  $V_{GS} = -1$ V and with four different values of the input power: -10.8 dBm, -5.8 dBm, -0.8 dBm, and 4.2 dBm.

Fig. 10. Comparison between measured (symbols) and simulated (lines) output power and  $b_2/a_1$  phase versus input power for a GaAs pHEMT with a gate width of 300  $\mu$ m at  $f_0 = 38$  GHz (a) and 42 GHz (b),  $V_{DS} = 0$  V, and  $V_{GS} = -1$  V.

## 5. Model validation based on cold-FET mixer design

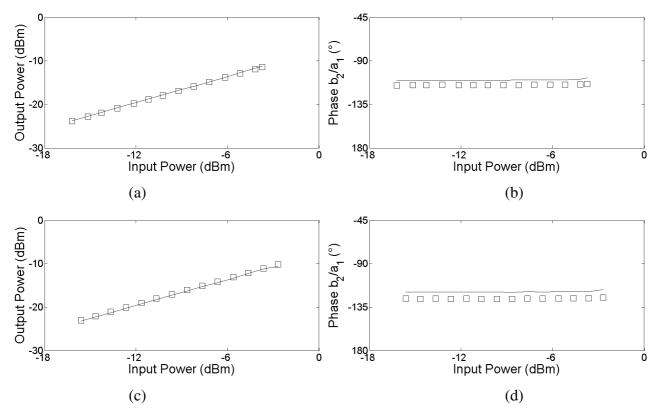

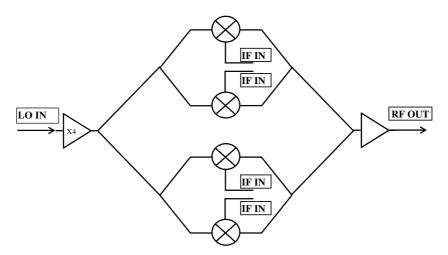

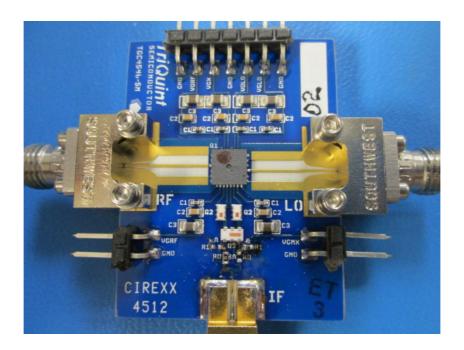

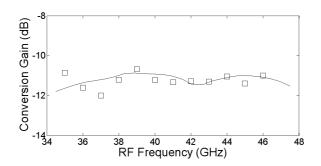

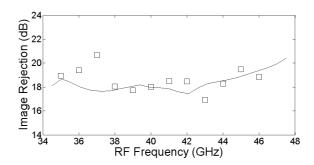

To definitely validate the developed model, simulations and measurements of a cold-FET mixer are reported. The mixer is part of a packaged Q-band up-converter (see Fig. 11), which integrates on the same MMIC two single balanced cold-FET mixers in I/Q configuration, a frequency quadrupler, which is able to convert the X-band LO input into the Q-band pump signal (PS) required for the mixers, and a four-stage RF driver, cascaded to the cold FET mixers [51]. A photograph of the designed up-converter is presented in Fig. 12. In order to better relate the cold-FET model accuracy with the measurements, the comparisons are performed between the stand alone measured mixer and the corresponding simulated circuit. In Figs. 13 and 14 the simulated performance of the designed up-converter is compared with the data obtained from scalar measurements. In particular, the conversion gain and the

image rejection are reported in Figs. 13 and 14, respectively. Also in this case, the model prediction capability is successfully confirmed.

Fig. 11. Block diagram of the designed Q-band up-converter.

Fig. 12. Photograph of the designed Q-band up-converter.

**Fig. 13.** Comparison between measured (symbols) and simulated (lines) conversion gain of the upconverter with an LO power of 14 dBm and an IF frequency of 2.5 GHz.

**Fig. 14.** Comparison between measured (symbols) and simulated (lines) image rejection of the upconverter with an LO power of 14 dBm and an IF frequency of 2.5 GHz.

### 6. Conclusion

This study has been devoted to the extraction of a nonlinear equivalent circuit of GaAs pHEMTs for mixer design. The developed approach, which is based on a straightforward extraction technique and transistor representation, leads to accurate and robust results. The model has been determined by using a purely analytical approach without any optimization and its representation has been based on look-up tables. The robustness of the achieved model has been confirmed by its capability to accurately predict the measured nonlinear device behavior for different gate widths and under different operating conditions: bias point, frequency, and input power level. Finally, to definitely validate the developed modeling approach, the extracted model has been used for the design of a packaged Q-band upconverter based on cold-FET mixer and a good agreement has been obtained between its measured and simulated performance.

### Acknowledgments

The authors would like to thank TriQuint Semiconductor for supplying the devices. This work was supported by the project PON 01\_01322 PANREX with financial support by Italian MIUR, FWO – Vlaanderen (Belgium), and EMRP 'HF Circuits' project.

### References

- [1] Y. Rolain, W. Van Moer, G. Vandersteen, and J. Schoukens, "Why are nonlinear microwave systems measurements so involved?" *IEEE Trans. Instrum. Meas.*, vol. 53, no. 3, pp. 726-729, Jun. 2004.

- [2] J. Verspecht "Large-signal network analysis," *IEEE Microw. Mag.*, vol. 6, no. 4, pp. 82-92, Dec. 2005.

- [3] W. Van Moer and Y. Rolain, "A large-signal network analyzer: Why is it needed?," *IEEE Microw*. *Mag.*, vol. 7, no. 6, pp. 46-62, Dec. 2006.

- [4] S. Maas, The RF and microwave circuit design cookbook. Norwood, MA, USA: Artech House, 1998.

- [5] D. Resca, A. Raffo, S. Di Falco, F. Scappaviva, V. Vadalà, and G. Vannini, "X-band GaN MMIC HPA for SAR systems designed by exploiting low-frequency load-line measurements," *IEEE Microw. Wireless Comp. Lett.*, vol. 24, no. 4, pp. 266-268, Apr. 2014.

- [6] P. Colantonio, F. Giannini, and E. Limiti, High efficiency RF and microwave solid state power amplifiers. Somerset, NJ, USA: John Wiley & Sons, 2009.

- [7] J. C. Pedro and S. A. Maas, "A comparative overview of microwave and wireless power amplifier behavioral modeling approaches," *IEEE Trans. Microw. Theory Tech.*, vol. 53, no. 4, pp. 1150-1163, Apr. 2005.

- [8] M. C. Tu, Y. C. Wang, and H. Y. Ueng, "Performance optimizing on multi-function MMIC design," *Microelectron. Eng.*, vol. 86, no. 10, pp. 2114-2118, Oct. 2009.

- [9] I. Angelov, H. Zirath, and N. Rorsman, "A new empirical nonlinear model for HEMT and MESFET devices," *IEEE Trans. Microw. Theory Tech.*, vol. 40, no. 12, pp. 2258-2266, Dec. 1992.

- [10]I. Angelov, L. Bengtsson, and M. Garcia, "Extensions of the Chalmers nonlinear HEMT and MESFET model," *IEEE Trans. Microw. Theory Tech.*, vol. 44, no. 10, pp. 1664-1674, Oct. 1996.

- [11]V. I. Cojocaru, and T. J. Brazil "A scalable general-purpose model for microwave FET's including DC/AC dispersion effects," *IEEE Trans. Microw. Theory Tech.*, vol. 45, no. 12, pp. 2248-2255, Dec. 1997. [12]A. Siligaris, G. Dambrine, D. M. M.-P. Schreurs, and F. Danneville, "A new empirical nonlinear model for sub-250 nm channel MOSFET," *IEEE Microw. Wireless Comp. Lett.*, vol. 13, no. 10, pp. 449-451, Oct. 2003.

- [13]S. Kabra, H. Kaur, S. Halder, M. Gupta, and R. S. Gupta, "Temperature dependent analytical model of sub-micron GaN MESFETs for microwave frequency applications," *Solid-State Electron.*, vol. 52, no. 1, pp 25-30, Jan. 2008.

- [14] R. Touhami, M. C. E. Yagoub, and H. Baudrand, "Comparing the MESFET and HEMT models for efficient circuit design," *Int. J. Numer. Model. El.*, vol. 20, no. 3, pp. 149-161, May/Jun. 2007.

- [15] G. Avolio, D. M. M.-P. Schreurs, A. Raffo, G. Crupi, I. Angelov, G. Vannini, and B. Nauwelaers, "Identification technique of FET model based on vector nonlinear measurements," *Electron. Lett.*, vol. 47, no. 24, pp. 1323-1324, Nov. 2011.

- [16]S. Khandelwal and T. A. Fjeldly, "Analysis of drain-current nonlinearity using surface-potential-based model in GaAs pHEMTs," *IEEE Trans. Microw. Theory Tech.*, vol. 61, no. 9, pp. 3265-3270, Sep. 2013.

- [17]D. E. Root, S. Fan, and J. Meyer, "Technology independent large signal non quasistatic FET models by direct construction from automatically characterized device data," *Eur. Microw. Conf.*, Stuttgart, Germany, Sep. 1991, pp. 927-932.

- [18]E. P. Vandamme, D. M. M.-P. Schreurs, C. van Dinther, G. Badenes, and L. Deferm, "Development of a RF large signal MOSFET model, based on an equivalent circuit, and comparison with BSIM3v3 compact model," *Solid-State Electron.*, vol. 46, no. 3, pp 353-360, Mar. 2002.

- [19]M. Myslinski, D. M. M.-P. Schreurs, and W. Wiatr, "Development and verification of a non-linear look-up table model for RF Silicon BJTs," *Eur. Gallium Arsenide and Other Semicond. Appl. Symp.*, Milano, Italy, Sep. 2002, pp. 93-96.

- [20]A. Orzati, D. M. M.-P. Schreurs, L. Pergola, H. Benedickter, F. Robin, O. J. Homan, et al., "A 110-GHz large-signal lookup-table model for InP HEMTs including impact ionization effects," *IEEE Trans. Microw. Theory Tech.*, vol. 51, no. 2, pp. 468-474, Feb. 2003.

- [21]M. C. Currás-Francos, "Comparison of HEMT non-linear model extraction approaches based on small signal and on large signal measurements," *Int. J. Numer. Model. El.*, vol. 16, no. 1, pp. 41-51, Jan./Feb. 2003.

- [22]G. Crupi, D. Schreurs, D. Xiao, A. Caddemi, B. Parvais, A. Mercha, and S. Decoutere, "Determination and validation of new nonlinear FinFET model based on lookup tables," *IEEE Microw*. *Wireless Comp. Lett.*, vol. 17, no 5, pp. 361-363, May 2007.

- [23]G. Crupi, D. M. M.-P. Schreurs, A. Caddemi, I. Angelov, M. Homayouni, A. Raffo, G. Vannini, and B. Parvais, "Purely analytical extraction of an improved nonlinear FinFET model including non-quasi-static effects," *Microelectron. Eng.*, vol. 86, no. 11, pp. 2283-2289, Nov. 2009.

- [24]G. Crupi, D. M. M.-P. Schreurs, J.-P. Raskin, and A. Caddemi, "A comprehensive review on microwave FinFET modeling for progressing beyond the state of art," *Solid-State Electron.*, vol. 80, pp 81-95, Feb. 2013.

- [25]G. Crupi, A. Raffo, G. Sivverini, G. Bosi, G. Avolio, D. M. M.-P. Schreurs, A. Caddemi, and G. Vannini "Non-linear look-up table modeling of GaAs HEMTs for mixer application," *IEEE International Workshop on Integrated Nonlinear Microwave and Millimetre-Wave Circuits*, Dublin, Ireland, Sep. 2012, pp. 1-3.

- [26]D. Schreurs, Y. Baeyens, B. K. J. C. Nauwelaers, W. De Raedt, M. Van Hove, and M. Van Rossum, "S-parameter measurement based quasistatic large-signal cold HEMT model for resistive mixer design," *Int. J. Microw. Mill.-Wave Comput.-Aid. Eng.*, vol. 6, no. 4, pp. 250-258, Jul. 1996.

- [27]V. Rizzoli, and A. Costanzo, "An accurate FET model suitable for general nonlinear and power applications," *Int. J. RF Microw. Comput.-Aid. Eng.*, vol. 10, no. 1, pp. 43-62, Jan. 2000.

- [28]K. Yhland, N. Rorsman, M. Garcia, and H. F. Merkel, "A symmetrical nonlinear HFET/MESFET model suitable for intermodulation analysis of amplifiers and resistive mixers," *IEEE Trans. Microw. Theory Tech.*, vol. 48, no. 1, pp. 15-22, Jan. 2000.

- [29]J. Xu, D. Gunyan, M. Iwamoto, J. M. Horn, A. Cognata, and D. E. Root, "Drain-source symmetric artificial neural network-based FET model with robust extrapolation beyond training data," *IEEE Int. Microw. Symp. Dig.*, Honolulu, HI, Jun. 2007, pp. 2011-2014.

- [30] V. Di Giacomo, A. Santarelli, A. Raffo, P. Traverso, D. Schreurs, J. Lonac, D. Resca, G. Vannini, F. Filicori, and M. Pagani, "Accurate nonlinear electron device modeling for cold FET mixer design," *Eur Microw. Integr. Circ. Conf.*, Amsterdam, The Netherlands, Oct. 2008, pp. 294-297.

- [31]0.15-µm power pHEMT 3MI, process data sheet, TriQuint Semiconductor, 2007.

- [32] Advanced Design System (ADS) Agilent. Ansoft Designer User Manuals.

- [33]G. Crupi and D. M. M.-P. Schreurs, Microwave de-embedding: from theory to application. Oxford, UK: Academic Press, 2013.

- [34]G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small-signal equivalent circuit," *IEEE Trans. Microw. Theory Tech.*, vol. 36, no. 7, pp. 1151-1159, Jul. 1988.

- [35]G. Crupi, D. M. M.-P. Schreurs, A. Raffo, A. Caddemi, and G. Vannini, "A new millimeter wave small-signal modeling approach for pHEMTs accounting for the output conductance time delay," *IEEE Trans. Microw. Theory Tech.*, vol. 56, no. 4, pp. 741-746, Apr. 2008.

- [36]J. Lu, Y. Wang, L. Ma, and Z. Yu, "A new small-signal modeling and extraction method in AlGaN/GaN HEMTs," *Solid-State Electron.*, vol. 52, no. 1, pp. 115-120, Jan. 2008.

- [37]M. Emam, J. C. Tinoco, D. Vanhoenacker-Janvier, and J.-P. Raskin, "High-temperature DC and RF behaviors of partially-depleted SOI MOSFET transistors," *Solid-State Electron.*, vol. 52, no. 12, pp. 1924-1932, Dec. 2008.

- [38]A. R. Alt, D. Marti, and C. R. Bolognesi, "Transistor modeling: Robust small-signal equivalent circuit extraction in various HEMT technologies," *IEEE Microw. Mag.*, vol. 14, no. 4, pp. 83-101, Jun. 2013.

- [39]L. Shen, B. Chen, and J. Gao, "An improved millimeter-wave small-signal modeling approach for HEMTs," *Int. J. RF Microw. Comput.-Aided Eng.*, vol. 24, no. 4, pp. 417-425, Sep. 2014.

- [40]S-W Moon, J-H Oh, Y-H Baek, M Han, J-K Rhee, and S-D Kim, "Millimeter-wave small-signal modeling with optimizing sensitive-parameters for metamorphic high electron mobility transistors," *Semicond. Sci. Technol.*, vol. 25, no. 8, pp. 1-7, Aug. 2010.

- [41]D. E. Root and B. Hughes, "Principles of nonlinear active device modeling for circuit simulation," *ARFTG Conf. Dig.*, Tempe, AZ, Dec. 1988, pp. 1-24.

- [42]G. Crupi, D. M. M.-P. Schreurs, A. Caddemi, A. Raffo, and G. Vannini, "Investigation on the non-quasi-static effect implementation for millimeter-wave FET models," *Int. J. RF Microw. Comput.-Aid. Eng.*, vol. 20, no 1, pp. 87-93, Jan. 2010.

- [43]C. Camacho-Penalosa, "Modeling frequency dependence of output impedance of a microwave MESFET at low frequencies," *Electron. Lett.*, vol. 21, no. 12, pp. 528-529, Jun. 1985.

- [44]F. Filicori, G. Vannini, A. Santarelli, A. M. Sanchez, A. Tazon, and Y. Newport, "Empirical modeling of low-frequency dispersive effects due to traps and thermal phenomena in III-V FET's," *IEEE Trans. Microw. Theory Tech.*, vol. 43, no. 12, pp. 2972-2981, Dec. 1995.

- [45]I. Kallfass, T. J. Brazil, B. OhAnnaidh, Peter Abele, T Hackbarth, M Zeuner, U. König, and H. Schumacher, "Large-signal modelling including low-frequency dispersion of n-channel SiGe MODFETs and MMIC applications," *Solid-State Electron.*, vol. 48, no. 8, pp. 1433-1441, Aug. 2004.

- [46]O. Jardel, F. De Groote, T. Reveyrand, J.-C. Jacquet, C. Charbonniaud, J.-P. Teyssier, D. Floriot, and R. Quéré, "An electrothermal model for AlGaN/GaN power HEMTs including trapping effects to improve large-signal simulation results on high VSWR," *IEEE Trans. Microw. Theory Tech.*, vol. 55, no. 12, pp. 2660-2669, Dec. 2007.

- [47]A. Raffo, S. Di Falco, V. Vadalà, G. Vannini, "Characterization of GaN HEMT low-frequency dispersion through a multiharmonic measurement system," *IEEE Trans. Microw. Theory Tech.*, vol. 58, no. 9, pp. 2490-2496, Sep. 2010.

- [48]A. Jarndal, P. Aflaki, L. Degachi, A. Birafane, A. Kouki, R. Negra, and F. M. Ghannouchi "Large-signal modelling including low-frequency dispersion of n-channel SiGe MODFETs and MMIC applications," *Solid-State Electron.*, vol. 54, no. 6, pp. 696-700, Jul. 2010.

[49]M. Gassoumi, M. M. Ben Salem, S. Saadaoui, B. Grimbert, J. Fontaine, C. Gaquiere, and H. Maaref, "The effects of gate length variation and trapping effects on the transient response of AlGaN/GaN HEMT's on SiC substrates," *Microelectron. Eng.*, vol. 88, no. 4, pp. 370-372, Apr. 2011. [50]S. D. Nsele, L. Escotte, J.-G. Tartarin, S. Piotrowicz, and S. L. Delage, "Broadband frequency dispersion small-signal modeling of the output conductance and transconductance in AlInN/GaN HEMTs," *IEEE Trans. Electron Dev.*, vol. 60, no. 4, pp. 1372-1378, Apr. 2013. [51]TGC4546-SM, upconverter data sheet, TriQuint Semiconductor, 2014.