Engineering Department of the University of Ferrara

Doctorate Degree in Science of Engineering

Coordinator: Prof. Stefano Trillo

Cycle: XXVI

# Methodologies and Toolflows for the Predictable Design of Reliable and Low-Power NoCs

ING-INF/01

Candidate:

Alberto Ghiribaldi

Advisor: Prof. Davide Bertozzi

## Contents

| $\mathbf{C}$ | onte  | $\mathbf{nts}$ |                                                     | j  |

|--------------|-------|----------------|-----------------------------------------------------|----|

| Li           | st of | f Figu         | res                                                 | V  |

| Li           | st of | f Table        | es                                                  | ix |

| $\mathbf{A}$ | ckno  | wledg          | rements                                             | 1  |

| 1            | Int   | roduc          | tion                                                | 3  |

| 2            | Des   | sign N         | Iethodologies for Fault-Tolerant NoC Design         | 7  |

|              | 1     | Moti           | vation                                              | 7  |

|              | 2     | Back           | ground                                              | 13 |

|              |       | 2.1            | The LBDR routing mechanism                          | 13 |

|              |       | 2.2            | Built-In Self-Test/Diagnosis Framework              | 15 |

|              | 3     | Fault          | z-Tolerant Architectures Under Test                 | 18 |

|              | 4     | The            | New Fault-Tolerant Flow Control                     | 20 |

|              |       | 4.1            | NACK/GO                                             | 20 |

|              |       | 4.2            | NACK/GO Operating Principle                         | 22 |

|              |       | 4.3            | Novel Low-Power Fault-Tolerant Arbiter              | 24 |

|              |       | 4.4            | Fault-Tolerance of Routing logic and Buffer FSMs    | 26 |

|              | 5     | Integ          | ration with Network-Level Fault Tolerance           | 26 |

|              | 6     | Glob           | al Strategy for Self-Configuration                  | 27 |

|              | 7     | Rout           | ing Primitive Architecture                          | 31 |

|              | 8     |                | erimental Results                                   | 34 |

|              |       | 8.1            | Area and Critical Path of the Fault-Tolerant Switch |    |

|              |       |                | Architectures                                       | 35 |

ii Contents

|   |      | 8.2                            | Power Consumption                                       | 37        |

|---|------|--------------------------------|---------------------------------------------------------|-----------|

|   |      | 8.3                            | Area Overhead of the Routing Primitive                  | 38        |

|   |      | 8.4                            | Fault tolerance of the routing primitive                | 39        |

|   |      | 8.5                            | Fault tolerance of the dual network                     | 41        |

|   |      | 8.6                            | Performance analysis                                    | 41        |

|   | 9    | Concl                          | lusions                                                 | 45        |

| 3 | Nor  | ı-Intrı                        | usive Trace & Debug NoC Architecture with Accu-         |           |

|   | rate | Time                           | estamping for GALS SoCs                                 | <b>47</b> |

|   | 1    | Motiv                          | vation                                                  | 47        |

|   | 2    | Relat                          | ed Work                                                 | 50        |

|   | 3    | Propo                          | osed Architecture and Topology                          | 50        |

|   | 4    | Times                          | stamping                                                | 54        |

|   | 5    | Resul                          | ts                                                      | 58        |

|   | 6    | Concl                          | lusion                                                  | 61        |

| 4 | ΑV   | ertica                         | lly Integrated and Interoperable Multi-Vendor Syn-      |           |

|   | thes | sis Flo                        | ow for Predictable NoC Design in Nanoscale Tech-        |           |

|   | nolo | ogies                          |                                                         | 63        |

|   | 1    | Motiv                          | vation                                                  | 63        |

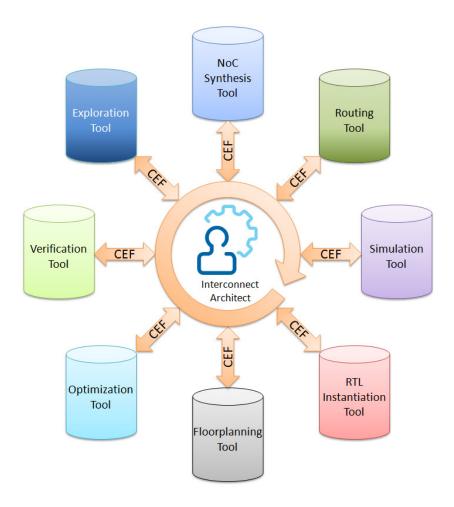

|   | 2    | CEF                            | File Format                                             | 66        |

|   | 3    | The H                          | Flow at a Glance                                        | 68        |

|   |      | 3.1                            | Front-End                                               | 69        |

|   |      | 3.2                            | Back-End                                                | 71        |

|   | 4    | Exper                          | rimental Results                                        | 73        |

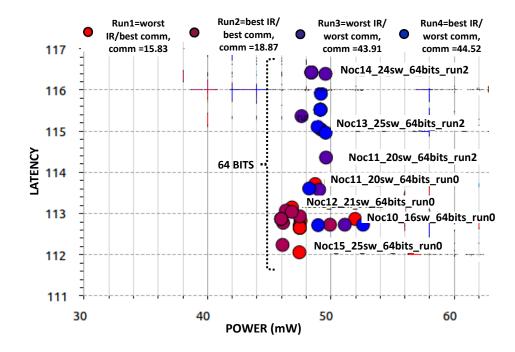

|   |      | 4.1                            | Floorplanning & Topology Synthesis, claims A and B $$ . | 74        |

|   |      | 4.2                            | Physical Convergence, claims A and C2                   | 76        |

|   |      |                                |                                                         |           |

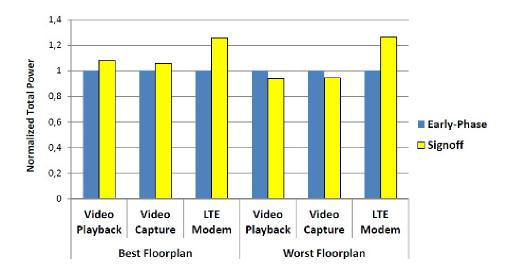

|   |      | 4.3                            | Correlation of Dynamic Power, claim B                   | 78        |

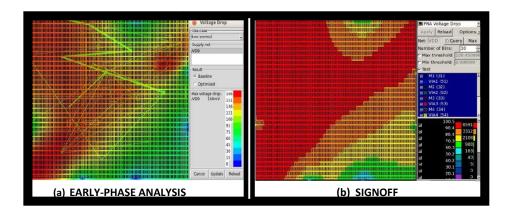

|   |      | 4.3<br>4.4                     | Correlation of Dynamic Power, claim B                   | 78<br>78  |

|   | 5    | 4.4                            | ·                                                       | 78        |

| 5 |      | 4.4<br>Concl                   | Correlation of IR Drop Maps, claim C1                   | 78        |

| 5 | АТ   | 4.4<br>Concl                   | Correlation of IR Drop Maps, claim C1                   | 78        |

| 5 | АТ   | 4.4<br>Concl<br>Cransite for C | Correlation of IR Drop Maps, claim C1                   | 78<br>79  |

Contents

|    | 3     | Switch  | Architecture                                    | 85 |

|----|-------|---------|-------------------------------------------------|----|

|    |       | 3.1     | Mousetrap Pipelines                             | 85 |

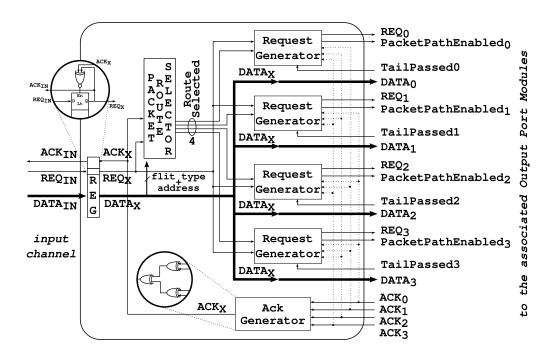

|    |       | 3.2     | Input Port Module Architecture                  | 86 |

|    |       | 3.3     | Output Port Module Architecture                 | 88 |

|    |       | 3.4     | 4-Input Mutex Design                            | 90 |

|    |       | 3.5     | Transition-Signaling Circular FIFO              | 91 |

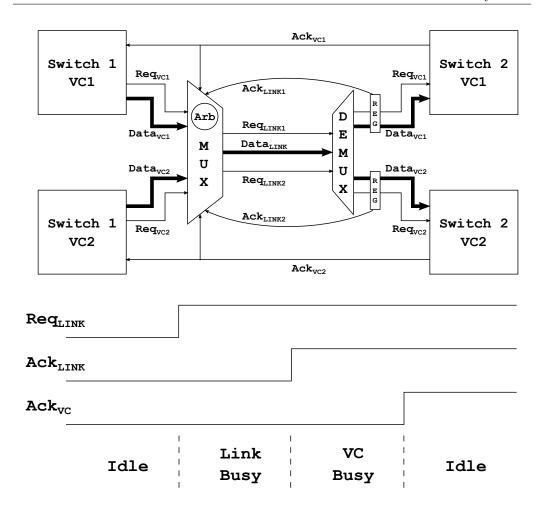

|    | 4     | Virtua  | l Channel Links                                 | 92 |

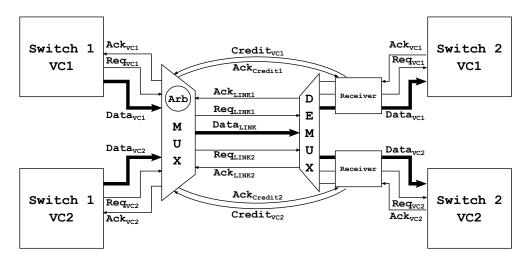

|    |       | 4.1     | First Solution: Credit-based flow-control       | 95 |

|    |       |         | Blocks detail                                   | 95 |

|    |       | 4.2     | Second Solution: Non-Blocking pipeline stages 9 | 97 |

|    |       |         | Blocks detail                                   | 98 |

|    |       | 4.3     | Timing Constraints                              | 00 |

|    | 5     | Semi-A  | automated Design Flow                           | 01 |

|    | 6     | Experi  | mental Results                                  | 04 |

|    |       |         | Experimental Setup                              | 04 |

|    |       |         | Comparative Analysis                            | 05 |

|    |       |         | NoC Link Effect                                 | 05 |

|    |       |         | Power Analysis                                  | 07 |

|    | 7     | Conclu  | sions                                           | 9  |

| 6  | Con   | clusion | ns 11                                           | L1 |

| Bi | bliog | graphy  | 11                                              | L3 |

| Αı | uthoi | r's Pub | lications List 12                               | 25 |

# List of Figures

| 2.1  | Baseline switch architecture. Not all connections are showed  | 13 |

|------|---------------------------------------------------------------|----|

| 2.2  | LBDR logic                                                    | 14 |

| 2.3  | The cooperative testing framework saving TPG instances and    |    |

|      | covering their faults                                         | 16 |

| 2.4  | The TMR optimized switch                                      | 19 |

| 2.5  | The optimized switch for error correction                     | 19 |

| 2.6  | NACK/GO switch architecture                                   | 20 |

| 2.7  | NACK/GO Flow control operation                                | 22 |

| 2.8  | Fault tolerant arbiter implementation                         | 25 |

| 2.9  | Topology of the dual network                                  | 28 |

| 2.10 | Configuration strategy at glance                              | 29 |

| 2.11 | Dual network routing primitive                                | 32 |

| 2.12 | TMR approach with per primitive voting system                 | 32 |

| 2.13 | Area comparison between TMR, ECC and NACK/GO switch.          | 34 |

| 2.14 | Critical path comparison between TMR, ECC and NACK/GO $$      |    |

|      | switch                                                        | 35 |

| 2.15 | Power consumption for idle, parallel and hotspot traffic con- |    |

|      | dition                                                        | 38 |

| 2.16 | NoC configuration: area overhead                              | 39 |

| 2.17 | Average configuration time (excluding the configuration algo- |    |

|      | rithm)                                                        | 43 |

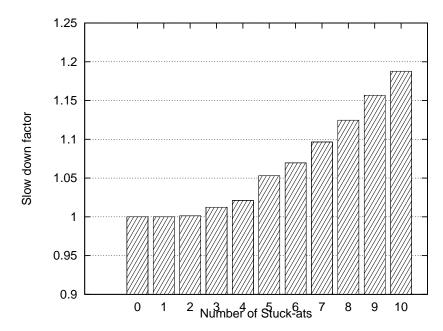

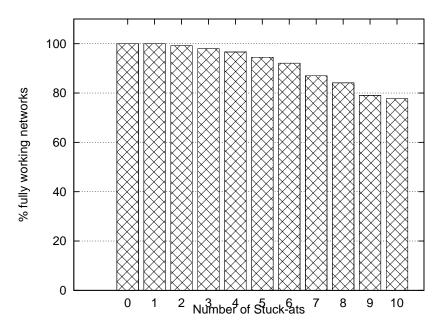

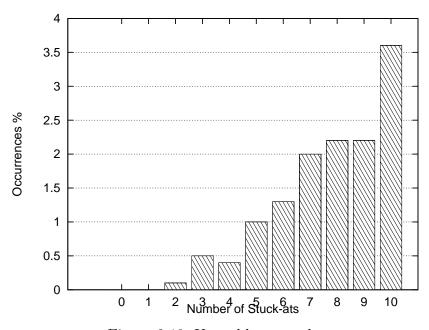

| 2.18 | Percentage of fully working networks (no switch excluded)     |    |

|      | varying the number of injected stuck-at faults                | 44 |

| 2.19 | Unusable network                                              | 44 |

| 3.1  | Hierarchical ring topology                                    | 49 |

**vi** List of Figures

| 3.2  | Transmission of a weight change packet $\pi_{\Delta}$          | 53  |

|------|----------------------------------------------------------------|-----|

| 3.3  | Weight adjustment                                              | 54  |

| 3.4  | 10-bit counter                                                 | 56  |

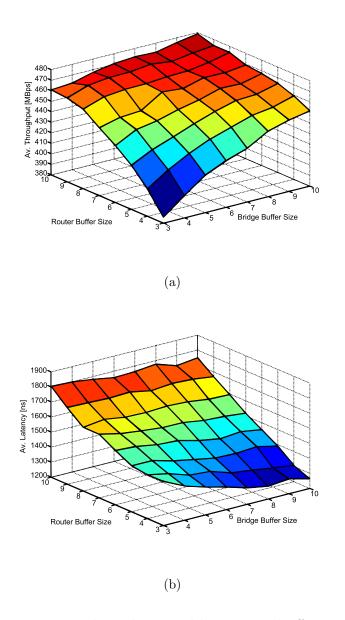

| 3.5  | Throughput and latency vs. buffer size                         | 59  |

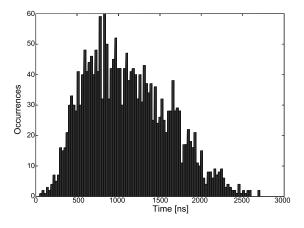

| 3.6  | Latency histogram                                              | 60  |

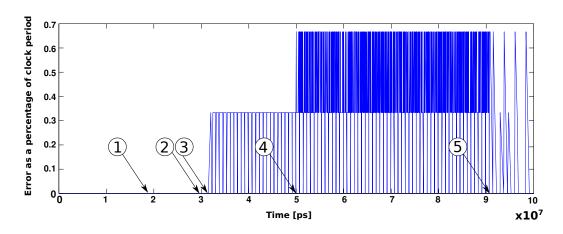

| 3.7  | Power up error                                                 | 61  |

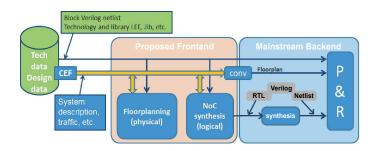

| 4.1  | CEF-enabled interoperability between NoC design tools          | 68  |

| 4.2  | Proposed flow for the implementation of application-specific   |     |

|      | NoCs targeting heterogeneous systems                           | 69  |

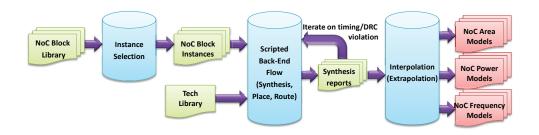

| 4.3  | NoC Topology Synthesizer: block characterization flow          | 70  |

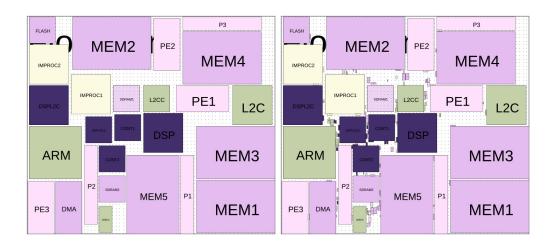

| 4.4  | The NoC synthesizer inserts the NoC blocks into input floor-   |     |

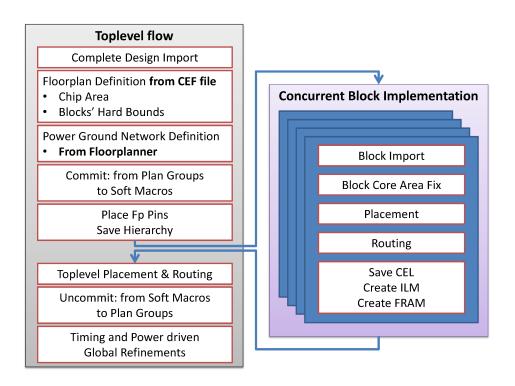

|      | plan by minimally perturbing block positions                   | 72  |

| 4.5  | Concurrent Hierarchical Layout Generation                      | 73  |

| 4.6  | Topologies generated by the Synthesizer engine for the various |     |

|      | floorplans for different flit widths                           | 75  |

| 4.7  | Correlation of NoC power between early-phase and post-layout   |     |

|      | analysis                                                       | 78  |

| 4.8  | Floorplan with best communication and best IR drop             | 80  |

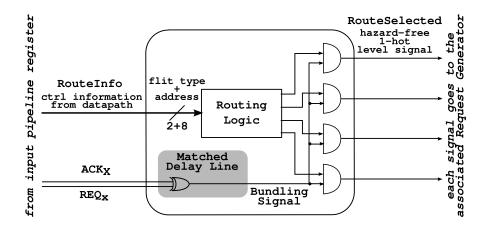

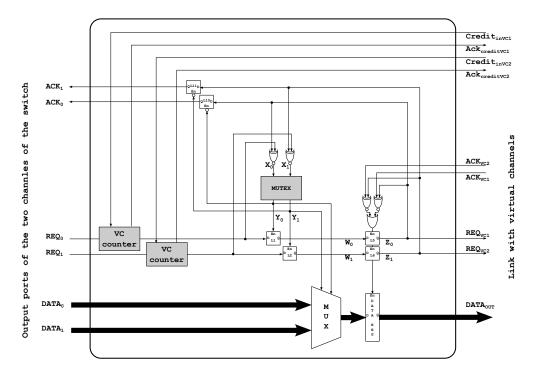

| 5.1  | Input Port Module                                              | 86  |

| 5.2  | Packet Route Selector                                          | 87  |

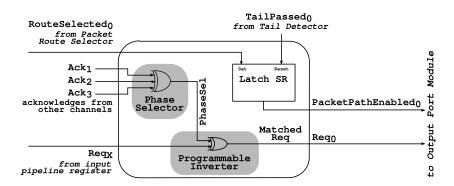

| 5.3  | Request Generator for Output Port Module 0                     | 88  |

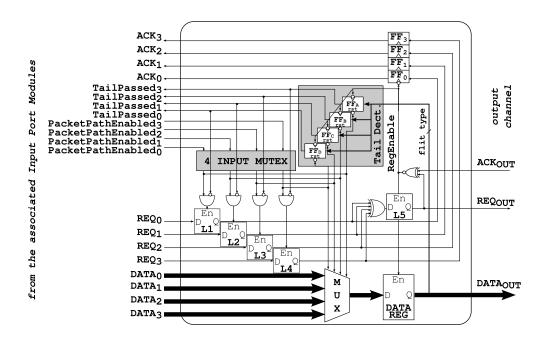

| 5.4  | Output Port Module                                             | 89  |

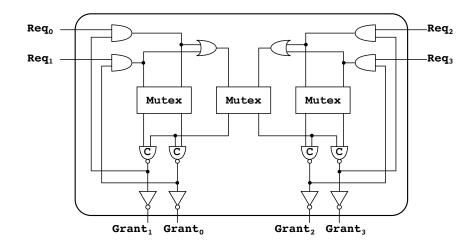

| 5.5  | Microarchitecture of new 4-input arbiter                       | 90  |

| 5.6  | Circular FIFO: top-level view                                  | 93  |

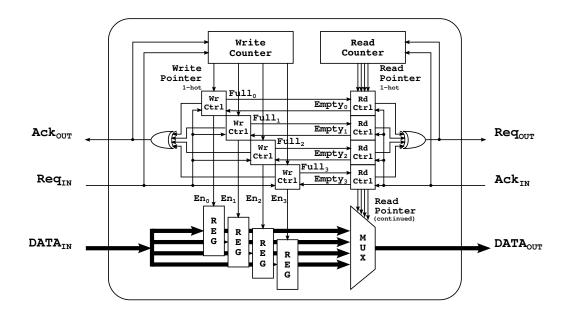

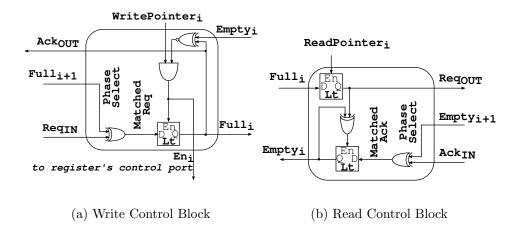

| 5.7  | Schematic of Write and Read Control Blocks                     | 93  |

| 5.8  | Virtual Channel, initial idea                                  | 94  |

| 5.9  | Virtual Channel, Credit-based                                  | 95  |

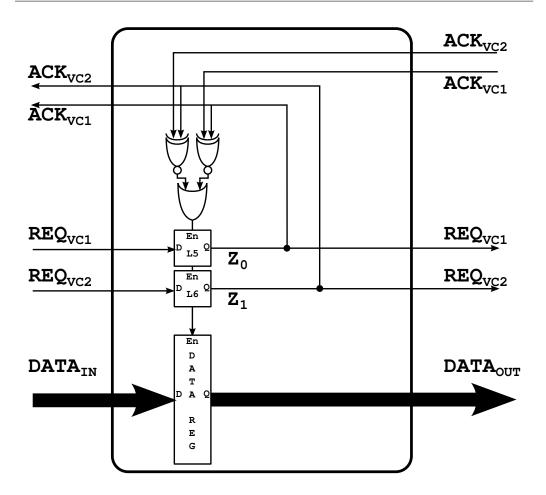

| 5.10 | Virtual Channel Credit-based, Arbitration Module               | 96  |

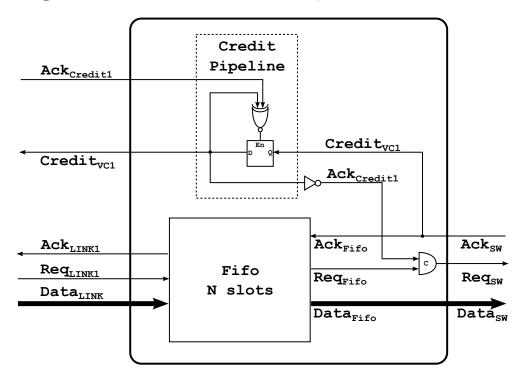

| 5.11 | Virtual Channel Credit-based, Virtual Channel Counter          | 97  |

| 5.12 | Virtual Channel Credit-based, Receiver Module                  | 97  |

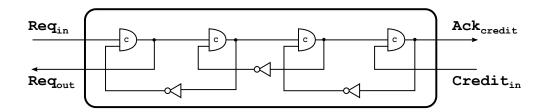

| 5.13 | Virtual Channel Credit-based, Pipeline Stage                   | 98  |

| 5.14 | Virtual Channel Non-Blocking, Pipeline Stage                   | 96  |

| 5.15 | Virtual Channel Non-Blocking, Pipeline Stage                   | 100 |

| T · · · C · · · | • •  |

|-----------------|------|

| List of Figures | 3/11 |

| List of Figures | V 11 |

|                 |      |

| 5.16 | Virtual Channel Non-Blocking, Pipeline Stage 101                                                               |

|------|----------------------------------------------------------------------------------------------------------------|

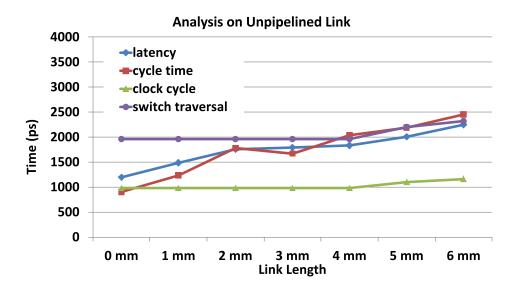

| 5.17 | Performance results with unpipelined links                                                                     |

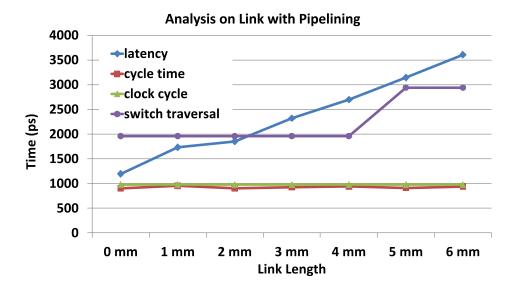

| 5.18 | Performance results with link pipelining                                                                       |

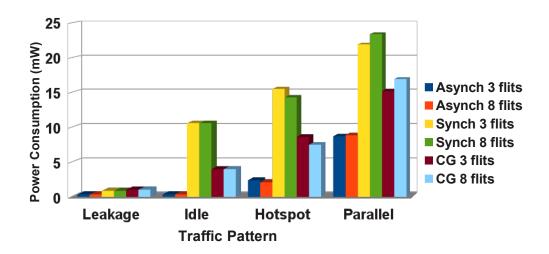

| 5.19 | Power consumption of the different switch architectures, vary-                                                 |

|      | ing the traffic injected $\ \ldots \ $ |

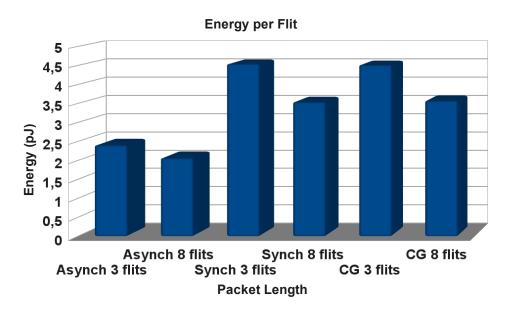

| 5.20 | Average energy required to propagate a Flit form input to                                                      |

|      | output                                                                                                         |

|      |                                                                                                                |

## List of Tables

| 2.1 | percentage of the input test patterns                          | 40  |

|-----|----------------------------------------------------------------|-----|

| 4.1 | Four selected reference floorplans in extreme corners with re- |     |

|     | gard to CommCost and IR-drop                                   | 74  |

| 4.2 | Main metrics of the four selected design points, one per input |     |

|     | floorplan, as estimated by the NoC Synthesizer                 | 76  |

| 4.3 | Timing convergence for all clock domains with proposed method- |     |

|     | ology, before and after Global Optimization                    | 77  |

| 5.1 | Asynchronous vs. Synchronous Switch                            | 105 |

### Acknowledgements

I would like to thank my advisor, Professor Davide Bertozzi, for his continuous support, motivation and guidance during my research and study. His limitless energy and enthusiasm in this journey together motivated all his Ph.D. Students, including me.

In addition, I would like to thank Professor Steven Nowick for taking me as an intern at Columbia University. This experience made me understood the importance of transmitting your knowledge and how to relate with your co-workers.

A special thank goes to all my lab friends here at the MPSoC research group in Ferrara. What started here is much more than just work together, but are experiences and moments I will never forget.

I am also grateful to my parents, for supporting me and directing me through all these years of University.

My deepest and genuine gratitude goes to my girlfriend Paola, for staying by my side during these years of Ph.D., no matter how tough it was.

## Chapter 1

### Introduction

In recent years, in order to overcome speed and power limitations of monolithic solutions, Chip Multi-Core and Many-Core have become a common practice in modern industrial landscape. Network-on-Chip (NoC) have been a clear key enabler for effective Multi-Core system integration, because they offer a regular and distributed structure on top of which different processing elements (cores, memories of accelerators) can be integrated, offering in this way the scalability and modularity that traditional shared buses could not achieve.

In the embedded system domain, a first possible solution to create these Multi-Core systems is by replicating in a regular way a basic computation tile, usually composed by a CPU and a memory bank, and its associated NoC switch element. These architectures lend themselves to become general purpose programmable accelerators or processing units, since the associated computational power is strictly related to the number of cores active at a time. At the opposite, if systems Multi-Core are designed for a specific target application domain, they usually feature custom heterogeneous devices, not only CPUs and memory banks but also other integrated blocks, such as peripherals controllers or graphic accelerators and so on, all interconnected by a custom NoC architecture.

However, there is today the unmistakable need to evolve design methodologies and toolflows for Network-on-Chip based embedded systems. In particular, the quest for low-power requirements is nowadays a more-than-ever urgent dilemma. Modern circuits feature billion of transistors, and neither power 4 Introduction

management techniques nor batteries capacity are able to endure the increasingly higher integration capability of digital devices. Besides, power concerns come together with modern nanoscale silicon technology design issues.

On one hand, system failure rates are expected to increase exponentially at every technology node when integrated circuit wear-out failure mechanisms are not compensated for. As a result, all systems – not only high-availability or mission-critical systems – must be designed for resilience. Being the communication backbone of the entire system, NoCs are very susceptible to permanent, intermittent and transient faults, since a single error in the network can put the whole system integrity at risk, jeopardizing its connectivity. However, error detection and/or correction mechanisms have a non-negligible impact on the network power, and if power-reliability trade-off is not properly accounted for upfront, the design outcome can be no longer viable for its excessive energy requirements.

On the other hand, to meet the stringent time-to-market deadlines, the design cycle of such a distributed and heterogeneous architecture must not be prolonged by unnecessary design iterations. In particular, it is mandatory that modern and future toolflows take into account back-end physical constraints, in order to find from the first design stages the correct placement of various blocks, in this way minimizing hotspots, enhancing communication traffic locality and paving the way for final timing convergence. This holds especially when considering Application-Specific Embedded Systems. In fact, being these systems built from many different IPs, system construction requires a custom-tailored Network-on-Chip topology synthesis. For application specific NoCs, the synthesis flow is key in order to reach the most predictable and power-efficient solution for the system at hand.

Overall, there is a clear need to better discriminate reliability strategies and interconnect topology solutions upfront, by ranking designs based on power metric. In this thesis, we tackle this challenge by proposing power-aware design technologies. First of all, we start analyzing design methodologies for cost-effective fault-tolerant NoC design, deriving the most suitable application for both General-Purpose and Application-Specific embedded systems. In the second place, we exploit these design methodologies for fault tolerance as a case study on top of which we develop a comprehensive and interoper-

able synthesis flow for Application-Specific Network-on-Chip, spanning from application requirements down to layout generation, dealing with Network-on-Chip design on nanoscale technologies with less design iterations.

Finally, we take into account the most aggressive and disruptive methodology for embedded systems with ultra-low power constraints. Since clock distribution itself represents a considerable amount of the whole power consumption of the entire system, our final goal is to migrate NoC basic building blocks to asynchronous (or clockless) design style, proposing a switch architecture that outperforms its synchronous counterpart in terms of energy-per-bit, power consumption and area footprint, while maintaining comparable performance with its synchronous counterpart. We deal with this challenge delivering a standard cell design methodology and mainstream CAD tool flows, in this way partially relaxing the requirement of using asynchronous blocks only as hard macros.

## Chapter 2

# Design Methodologies for Fault-Tolerant NoC Design

#### 1 Motivation

Modern integrated systems are increasingly multi-core, since congruent multiples in processing power are pursued by replicating processing engines on the same silicon die rather than by evolving the microarchitecture of monolithic processing cores. This latter approach has in fact historically resulted in diminishing returns. In this context, systems become susceptible to errors: even though replicated cores are available in such chip multiprocessors, they are not sufficient for providing system level fault protection due to the lack of fault tolerance and/or fault isolation in their shared components [1].

The system integration and communication infrastructure is certainly the most important of such shared components. For large scale systems, network-on-chip (NoC) architectures are today mainstream for global intra-chip communication: they facilitate the modular construction of many-core architectures, they provide communication abstractions and services across component boundaries and they enable the top-down design of highly power-manageable architectures.

As faults will appear with increasing probability due to the susceptibility of shrinking feature sizes to process variability, age-related degradation, crosstalk, and single-event upsets, designing efficient fault tolerant NoCs becomes a key requirement.

Transient faults cannot be handled by off-line strategies as they appear and disappear unpredictably. Fault-tolerant systems must be therefore employed to satisfy the high reliability constraints imposed by modern systems. In this direction, there are three major approaches.

First, Modular Redundancy can be adopted. For instance, Constantinides et al. demonstrated the BulletProof router, which efficiently uses N-modular redundancy (NMR) techniques for router level reliability [16]. However, NMR approaches are expensive, as they require at least N times the silicon area to implement. Additionally, network level reliability needs to be considered since some logic is impossible or expensive to duplicate (e.g., clock tree) or spares may run out, resulting in the loss of a router. Similarly, Time Redundancy (TR) [51] can be adopted to protect the NoC against faulty components. However, Time Redundancy decreases the performance of the NoC, since all information needs to be retransmitted.

Alternatively, error detecting codes can be used. The detection phase is followed by a recovery one, for instance based on the retry of the unsuccessful operation. Simple retransmission schemes are described in [18, 19]. In terms of implementation, [17,19] use a single transmission buffer that contains both sent and unsent flits together. [18] uses link-level retransmission together with the Unique Token Protocol (UTP) to ensure reliability. However, it requires at least two copies of a packet in the network, increasing buffer occupancy and flow control complexity. In contrast, [54] minimizes control logic by using a barrel shifter as retransmission buffer whose size is matched to the round trip notification latency of a NACK. The work in [37] targets virtual channel NoC implementations and uses dynamic packet fragmentation in tandem with a credit-based fault-tolerant flow control to recover from corrupted virtual channel states. In general, state-of-the-art in fault-tolerant flow control can be reviewed in [57], where the power inefficient ACK/NACK or the high-impact T-Error protocols are compared. The key take-away is that more research is needed in this domain, a challenge that for instance [37] takes on. Unfortunately, the solution in [37] comes with heavy throughput limitations. Finally, error correcting codes (ECC) can be employed. They typically allow the correction of a limited amount of errors per codeword in order to contain complexity. Nonetheless, they are commonly reported to introduce 2.1 Motivation 9

a high timing penalty, because of the delay of the encoder/decoder and correction blocks. In [83] the router selects on the fly the most effective ECC scheme to send the data trough the link. The work in [23] proposes to use the Hamming Code on the input buffers to protect FIFO data. Similarly [21] protects the data-path via an ECC strategy. However, by using the fault tolerance techniques proposed in [21, 23, 83], but also in [63] and [62], only the links are protected, and incur large area and performance overhead. A retransmission scheme that enables graceful degradation of NoC communication performance under high failure rates is proposed in [40], but again the control path is not protected. Interestingly, erroneous behaviour in the functionality of the routing process or in output port arbitration may cause flit/packet misrouting. In the worst case, this results into loss of information or even into a deadlock condition. Clearly, robust protection against such upsets should be provided. Finally, [15] adopts error correcting coding to perform on-line testing but achieves a quite low coverage (63%). [54] proposes a mechanism able to exploit an ECC strategy for single error correction and a retransmission procedure once a double error is revealed. Anyway, the area overhead to support such mechanism is really severe, in addition to the high switching activity suffered from the retransmission buffer.

In general, the use of ECC in the above approaches suffers from two main limitations. First, the corrector is used at each clock cycle and ends up in the critical path. Second, the proposed architectures are not robust to many transient faults affecting the corrector itself. Moreover, there is consensus on the fact that error detection followed by retransmission typically has a milder impact on network power than error correction. This is the assumption of the work in [40] and the result of an ad-hoc experimental framework in [10] and [50]. However, none of these works relies on accurate microarchitectural studies and on physical implementation efforts, which are instead the key contributions of this thesis, in combination with the switch-level integration of design methods for fault-tolerance.

On the other hand, the capability of surviving permanent faults in the network closely depends on the flexibility of the routing framework, including both a reprogrammable routing mechanism [45], a fault-tolerant routing algorithm [29] and a suitable combination thereof [60]. Most of the proposals

for fault-tolerant routing algorithms proposed so far for NoCs are based on programmable routing tables, storing the target output port to be taken by a packet for a given destination [53]. Unfortunately, table-based routing suffers from scalability limitations [61]. Above all, most fault tolerant routing frameworks do not address the testing problem: they just assume that faults are detected somehow on the fly and notified to the reconfiguration infrastructure [68].

The open literature offers a plethora of works tackling the problem of fault tolerance in the NoC domain. Unfortunately, most of them utilize distributed approaches which are inherently weak since they are deadlock prone or require flooding operations as well as the need to track several network status information thus calling for additional buffering resources. Zhang et al in [85] propose a topology reconfiguration strategy which is based on the concept of virtual topology. However, no discussion is provided regarding the reconfiguration mechanism of the entire system. In [33], a heuristic search algorithm for re-routing in on-chip network is presented. Unfortunately, the algorithm can not guarantee that every generated configuration is valid, therefore, a manual check is required. Authors in [2] present another rerouting algorithm which unfortunately does not guarantee 100% deadlock freedom, requires flooding strategies and increases the transmission time due to ping-pong re-routing. Furthermore, such an approach demands for considerable buffering resources in order to keep a history of all the packets traversing a switch. Configurable routing has been proposed in several forms, e.g., in [5], the authors propose a custom methodology, based on packet rerouting, to handle data transfers upon power management events or system faults. However, their approach is not general and is actually working around faults in the attached cores, not in the NoC itself. Deterministic routing is characterized by its simplicity and minimal overhead; it can be easily configured to avoid deadlocks [70] and natively guarantees in-order delivery. Unfortunately, deterministic routing does not adjust to the system evolution over time; on the contrary, dynamic routing has been proposed to achieve goals such as bypassing faulty nodes and minimizing congestion [3]. Dynamic routing needs decentralized decision processes and is therefore often achieved with dedicated logic in every router [9].

2.1 Motivation 11

This thesis considers the common fault-tolerance strategies for SEUs (error correction, error detection and retransmission, triple modular redundancy) and provides the needed support for them to a baseline NoC switch for use in the embedded computing domain. The microarchitecture-level approach taken by this thesis brought two key novelties. On one hand, we could clearly identify missing gaps in the current landscape of fault-tolerant switches, namely fault-tolerant flow control and on-demand correction, and propose new solutions for them. On the other hand, we were able to contrast retransmission oriented vs. correction oriented techniques by capturing their global switch level implications (both data path and control path) in an architecture homogeneous experimental setting. Also, physical implementation analysis enabled to consider key second-order effects from logic synthesis, placement and routing. Overall, this thesis delivers practical insights for the provision of SEU tolerance to NoCs in a power-constrained environment.

In addition, this thesis moves from the perspective that fault detection and system reconfiguration can not be considered two separate tasks but they need to be co-designed with each-other and along with the underlying system from the ground up, and not as an afterthought. In fact, relevant interdependencies exist between the two frameworks:

- (i) Testing and diagnosis granularity are dictated by the routing mechanism flexibility and by the hardware support for reliability in the network.

- (ii) Similarly, the amount of control information that needs to be reprogrammed upon fault detection depends on the routing mechanism and on the way it exposes flexibility.

- (iii) The place where responses to test patterns are analyzed and diagnosis information are computed has to be matched to the place where the course of action for network reconfiguration is taken. As an example, given a distributed built-in self-test (BIST) approach to NoC testing, failure patterns could be either notified to a global controller or directly used by a local mechanism for distributed reconfiguration. The system-level architectural implications in the two cases are radically different.

This thesis aims at overcoming the limitations stemming from the isolated development of testing and configuration strategies by **co-designing the** two strategies together for better optimization and by addressing the

system-level implications of implementing the entire fault-diagnosis and configuration procedure.

In particular, the contribution of this chapter can be detailed as follows:

- the complete hardware infrastructure for NoC fault-tolerance and configuration. We start from a baseline switch architecture featuring reconfigurable routing logic and built-in self-testing procedure, and we provide additional hardware support, spanning from three alternative solution for tackling SEUs up to the global infrastructure for control signaling. Above all, this thesis shows how all these components can be co-designed and specialized in the presence of a logic-based distributed routing (LBDR) mechanism, providing much better scalability to nanoscale technologies than forwarding tables from an area, power and delay viewpoint.

- the global configuration strategy orchestrating the operation of the hardware components together while at the same time implementing a mix of fault-tolerance and online testing strategies ensuring reliable communication between testing/diagnosis logic with the reconfiguration manager and viceversa. Primary objective of the design choices is to avoid flagging a corrupted NoC switch as operational because of faults in the configuration infrastructure. We opt for a centralized configuration mechanism where a global controller with full visibility of the network state is in charge of computing reconfiguration information for the routing mechanism in the switches.

- we provide accurate characterization of quality metrics of the proposed system infrastructure, which are typically overlooked in previous work or provided with lower accuracy (e.g., incomplete analysis, timing constraints for synthesis omitted) or under oversimplifying assumptions (e.g., single stuck-at faults). In particular, we assess incremental area overhead for BIST, diagnosis and for reconfiguration in an architecture-homogeneous experimental setting. Also, we perform fault simulation with a fault injector acting upon the gate level netlist of the configuration infrastructure and categorize the severity and occurrence probability of fault implications on the global configuration process.

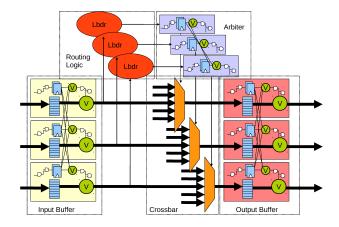

Figure 2.1: Baseline switch architecture. Not all connections are showed.

#### 2 Background

The switch architecture proposed in this work is a major extension of the baseline ×pipesLite switch [71], illustrated in Figure 2.1, which targets the embedded computing domain with a very lightweight architecture. It implements both input and output buffering and relies on wormhole switching. The crossing latency is 1 cycle in the link and 1 cycle inside the switch, a design point suitable for the embedded computing domain. The switch relies on a STALL/GO flow control protocol (see section 4).

The switch architecture is divided into a control path and a data path. Input buffers, crossbar multiplexers and output buffers belong to the data path, while port-arbiters, routing modules and buffer control logic belong to the control path. The switch implements logic-based distributed routing (LBDR [59]): instead of relying on routing tables, each switch has simple combinational logic that computes target output ports from packet destinations. The support for different routing algorithms and topology shapes is achieved by means of 26 configuration bits for the routing mechanism of the switch.

#### 2.1 The LBDR routing mechanism

There are two main reasons leading us to select logic-based distributed routing (LBDR) as the routing mechanism of choice for our target NoC.

First, routing logic features better delay and area scalability with respect to forwarding tables, both with technology scaling and with increase of network size [61]. For small network instances, only register-based memory macro implementations are competitive, however they increase with the network size, while LBDR logic only grows with the switch radix [59].

Second, it reduces the amount of signaling between the NoC switches and the configuration manager, since the routing logic partially retains its flexibility by means of few configuration bits (namely routing  $R_{xy}$ , connectivity  $C_x$  and deroute bits dr). The number of these bits (26 in the LBDR variant of this thesis) is orders of magnitude smaller than the size of a forwarding table, yet makes the routing mechanism reconfigurable.

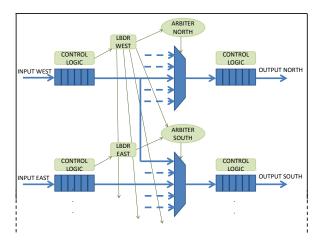

Figure 2.2: LBDR logic.

The core of LBDR logic is illustrated in Fig.2.2(a), showing the conditions that select the output port north UN' for packet routing. The routing decision is taken based on:

- the quadrant N'/S'/W'/E' of packet destination (whose ID is embedded into the incoming packet);

- the routing restrictions posed by a deadlock-free routing algorithm (coded by the *routing bits*);

- the switch connections with the rest of the network (coded by the *connectivity bits*).

For some failure patterns, LBDR may not be able to find a route for the packet. In that case, a couple of additional *deroute bits* feed a logic which computes a valid output port to reach the destination. This extends the fault coverage of LBDR, which in [59] was proved able to work in roughly 60% of the irregular topologies derived from a 2D mesh. A larger coverage would require the NoC to revert to virtual cut-through switching and is therefore left for future work.

It is worth recalling that LBDR is a routing mechanism that supports the most widely used routing algorithms for irregular topologies, including segment-based SR [46] routing. As proved in [59], whenever a faulty 2D mesh topology can be handled by LBDR (including its deroute capability), it is always possible to find a suitable SR instance that can be used in combination with LBDR to route that topology.

Simply, a fault detection is equivalent to a change in the topology, and the routing, connectivity and deroute bits of all the switches have to be programmed from scratch or incrementally updated with respect to the original fault-free scenario. In [59], this is on burden of a configuration algorithm, which needs the list of failed links to recompute the configuration bits for correct routing with the available communication resources. Failure of a switch input or output port (and associated internal logic) can be viewed as the failure of the connected link.

Next section will illustrate the Built-In Self-Testing and Self-diagnosis (BIST/BISD) strategy which meets this requirement and provides an indication of whether input and output ports of a switch are operational.

Also, later on in the thesis it will be presented how to establish a reliable bidirectional path from the testing logic to the configuration manager and finally to the routing logic to be reprogrammed.

#### 2.2 Built-In Self-Test/Diagnosis Framework

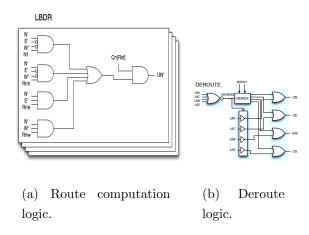

The key idea of our "Built-in Self-Test/Built-in Self-Diagnosis" (BIST/BISD) framework consists of exploiting the inherent structural redundancy of an on-chip network. We opt for testing the NoC switches in parallel, thus making test application time independent of the network size. Communication channels between switches are tested as a part of the switch testing framework.

Figure 2.3: The cooperative testing framework saving TPG instances and covering their faults.

Each switch can in turn test its several internal instances of the same subblocks (crossbar muxes, communication channels, port arbiters, routing modules) concurrently. In fact, all the instances are assumed to be identical, therefore they should output the same results if there is no fault. As a consequence, the test responses from these instances are fed to a comparator tree. This makes the successive diagnosis much easier. There is a unique test pattern generator (TPG) for all the instances of the same block, thus cutting down on the number of TPGs. Although the principle is similar to what has been proposed in [4,6,31], there is a fundamental difference. If the TPG of a set of block instances is affected by a fault, then the comparison logic will not be able to capture this since all instances provide the same wrong response. To avoid this, a cooperative framework is devised, such that each switch tests the block instances of its neighboring switches [73].

As an example, a switch tests the incoming communication channels from its north/south/west/east neighbors (i.e., it feeds their test responses to its local comparator tree), thus checking the responses to distinct instances of the same TPG. This way, a non-null coverage of TPG faults becomes feasible. Fig.2.3(a) clearly illustrates the cooperative testing framework for communication channels and the need for a single TPG instance per switch to feed test patterns to all of its output ports. Faults in the TPG, in the output buffer, in the link and in the input buffer will be revealed in the downstream

switch. Each switch ends up testing its input links, while its output links will be tested by their respective downstream switches.

The same principle can be applied for the testing of switch internal block instances associated with each output port: crossbar muxes and output port arbiters. Fig.2.3(b) shows the case of port arbiters. The main requirement for testing these instances is that the communication channels bringing test responses to the comparators in the downstream switches are working correctly. Clearly, testing these modules can only occur after communication channels have been tested. Therefore, the procedures in Fig.2.3(a) and Fig.2.3(b) occur sequentially in time. Should one communication channel result defective, this would not be a problem, since it would not make any sense to test and use a port arbiter when the corresponding port is not operational. Crossbar multiplexers associated with each output port are tested in the same way and are hereafter not illustrated in Fig.2.3 for lack of space.

Inspired by such cooperative approach applied to the testing of channels and arbiters, we now extend such principle also to test block instances associated with each switch input port with some modifications. This is the case of the LBDR routing block. The key idea to preserve the benefits of cooperative and concurrent testing is to carry test patterns rather than test responses over the communication channels to neighboring switches, where the LBDR instances are stimulated and their responses compared (see Fig.2.3(c)). If the channel is not working, testing and using the downstream routing block is useless, since it is associated with an input port that will not be used.

On a cycle by cycle basis, comparator outputs are fed to a diagnosis logic which identifies where exactly the fault occurred. In our diagnosis framework, each switch checks whether test responses from its input ports are correct or not. As a consequence, the outcome of the diagnosis is coded in only 5 bits, one for each input port of the current switch (they would be of course doubled if a two-rail code is implemented to protect them against stuck-at faults). A '1' indicates that the port is faulty. In practice, the fault may be located either in the input buffer or in the LBDR module, in the connected communication link or even in the output buffer and associated port arbiter and crossbar multiplexer of the upstream switch. This further level of detail is not needed, since in any case the key take-away is that the link is unusable,

and this is enough for a global controller to recompute the configuration bits for the LBDR mechanism. In the final implementation, other 5 bits will be needed to code the diagnosis outcome because of practical implementation issues associated with network flow control. Further details on this can be found in [73].

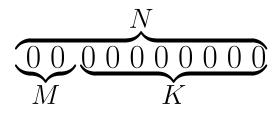

After the testing procedure has been completed, 10 bits are produced by each switch and have to be fed to the actual configuration infrastructure. Next section motivates the choice of our centralized approach and details the architecture of the configuration infrastructure, which is centered around a dual network for signaling of control information between switches and the controller and vice versa (see Fig 2.9).

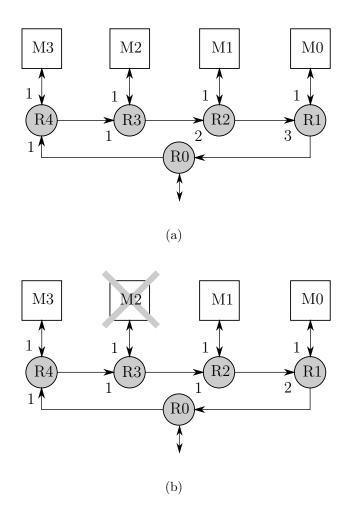

#### 3 Fault-Tolerant Architectures Under Test

This thesis considers and compares, at the microarchitecture and post place & route levels, three main approaches for SEU tolerance.

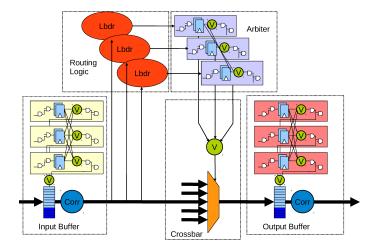

The three improved versions analyzed in this thesis are:

- (1) Triple Modular Redundancy (TMR). In this architecture, links as well as switch data lanes are triplicated (Fig.2.4). As regards its control path, voting is performed for the registers of every finite state machine, to prevent a transient fault from misaligning their states. The TMR architecture can afford using the native STALL/GO flow control. This is the reference solution for fault-tolerance used for the sake of comparison.

- (2) Error Correcting Switch Architecture. This solution is illustrated in Figure 2.5. Error correctors are used at every clock cycle both at the level of switch-to-switch communications and for intra-router data path operation. Concerning the control path, TMR is applied both to buffer FSMs and to routing logic/arbiters. Since correctors are enabled at every clock cycle and lie on the switch critical path, they introduce severe switching activity and delay penalty. In contrast, solutions based on ECCs are typically advocated by those designers who cannot stand the retransmission latency in spite of its low occurrence probability.

- (3) NACK-GO Switch Architecture. In this retransmission-oriented solution, a fault-tolerant flow control protocol (NACK/GO) is used on the data path

Figure 2.4: The TMR optimized switch.

Figure 2.5: The optimized switch for error correction.

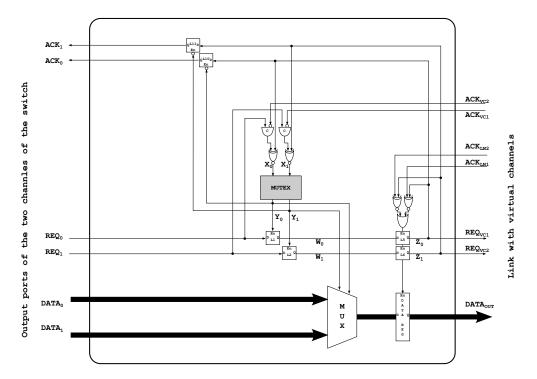

to notify error detection and trigger link-level data retransmissions, and also on the internal switch data path, to ask for data retransmissions from switch input to output buffers. The switch architecture is illustrated in Fig.2.6. Interestingly, on-demand correctors are used to repair corrupted values in the source buffers, which a retransmission would not fix. Thanks to the retransmission capability of the data path, the control path can implement a simpler dual-modular redundancy: in case of differences between the replicated paths, the current transfer is invalidated and a retransmission is required in the next cycle (see section 4.3). Next, the NACK/GO protocol is derived, and later on the control path is detailed accordingly.

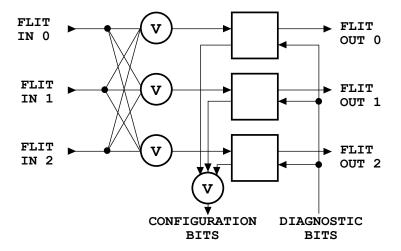

Figure 2.6: NACK/GO switch architecture.

#### 4 The New Fault-Tolerant Flow Control

#### 4.1 NACK/GO

STALL/GO is one of the simplest flow control protocols that can be found in the open literature. It leverages only one forward signal, that flags the availability of new valid data (Valid signal) and one backward signal, used to stop the communication flow when a new flit cannot be accepted due to congestion in the downstream node (Stall signal). Conversely, ACK/NACK is a flow control protocol with error detection/notification capabilities. It exploits a Go-back-N policy to manage and control correctness of the transmitted data. When an error is detected in a transmitted flit, the receiver signals this event to the sender, who will retransmit the flit with the corrupted information and all the (N) successive ones.

Unfortunately, the ACK/NACK protocol does not make a clear distinction between the backpressure phenomenon and the occurrence/detection of transient faults. As a consequence, a nack received by the upstream switch means that the flit should be retransmitted for some reason. In case of congestion of downstream paths, the protocol keeps retransmitting the same flit indefinitely regardless of the receiver state, thus proving power-inefficient. On the contrary when a STALL/GO protocol is considered then transmission freezes until a go arrives, in case a stall notification is received upstream. This protocol is much more power efficient but does not provide any kind of support

for fault tolerance and data retransmission.

Augmenting the protocol in this direction was one key objective of this thesis, thus coming up with the NACK/GO flow control protocol. NACK/GO is a new protocol, and associated switch implementation, that offers full error detection and notification capabilities of ACK/NACK while preserving the power efficiency of STALL/GO for error-free operation.

NACK/GO leverages four control signals to control transmission of data and achieve fault tolerance. There are two signals going in the same direction of the data stream, and two backward propagating signals.

**Valid**: this signal flags availability of new data, and it triggers the data transfer.

**Trash**: this control signal notifies that the data currently being transmitted is corrupted and should be discarded. The reason why the valid signal is not used for this is to optimize the internal critical path of the switch and avoid multi-cycle switch traversal.

**Stall**: it stalls the transmission in case of traffic congestion. The Stall signal stops the communication flow, freezing all the forwarding control signals and data to their current value.

**Nack**: Nack signal is de-asserted low when a valid flit has been received in the previous clock cycle (Acknowledgement). In contrast, Nack is asserted high whenever no valid flit is received, either because no transmission took place or because the accepted flit is detected as corrupted.

NACK/GO combines the best of STALL/GO and ACK/NACK.

Like STALL/GO, it exploits an efficient methodology to block the communication traffic in case of congestion, avoiding the unnecessary switching activity for flit retransmission as in ACK/NACK. It uses a signal to notify the availability of free buffer positions inside the receiver, so communication can be frozen when congestion occurs. Furthermore, a Stall signal avoids the roundtrip necessary to resume communication from the packet that was not accepted like in ACK/NACK, leading to a better average performance.

In addition, it features the error flagging capability not exposed by STALL/GO. In this way the system can re-establish a correct working point and resume its correct operating condition.

These advantages come at the cost of extra channel wiring, since a total

Figure 2.7: NACK/GO Flow control operation

of 4 control signals are needed, rather than the 2 of STALL/GO, and a more complex control logic inside the buffers and the switches. NACK/GO features worse minimum buffer slot requirements than STALL/GO, since it requires a minimum of 3 buffer slots. In addition, every pipeline stage inside the link should have not only flow control capabilities, but also error detection/correction capabilities. For this reason, every repeater must have at least three buffer positions, more than the two required for STALL/GO.

#### 4.2 NACK/GO Operating Principle

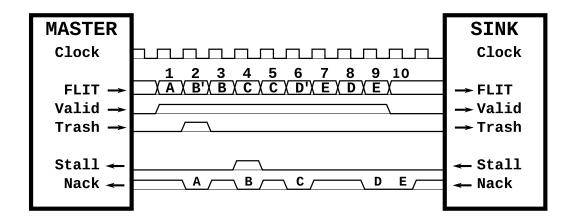

In order to describe the details of the NACK/GO operating principle, this section will suppose a communication taking place between an upstream node M (master) and a destination node S (sink), as illustrated in Fig.2.7. The master node sends 5 data flits, named from A to E.

Clock cycle 1 The source node M has a new data available. It will begin the transfer by flagging the possibility to send a new flit, A, asserting the Valid control signal high. The destination node S will communicate its availability to receive the incoming transmission by asserting the Stall backward control signal low. In such a configuration, the flit A is successfully transferred from Master to Sink. It is however not possible to discard it in the Master node M yet, since it is still waiting for the acknowledgement from the destination that will take place in the next clock cycle.

Clock cycle 2 The source node tries to send the next flit available, B. Suppose that while transmitting, the sender detects an error inside B (i.e., it

has received an incorrect flit from its upstream node, which is speculatively sent to S while performing error detection in parallel). The sender will notify that the ongoing flit is corrupted with the Trash signal in case of mispeculation. The receiver S will receive the B flit, but this will not be stored. The transmission of the flit is discarded, and the source will start the appropriate procedure to recover and re-establish the correctness of flit B before transmitting it again. In the meantime, destination S will check the A flit, received in the previous clock cycle. Since no error is detected, the Nack signal is de-asserted low.

Clock cycle 3 After an arbitrary number of clock cycles (not showed here), in which the Valid signal has been de-asserted low, Master has a new version of B, and can transmit it. It signals the transmission using Valid signal, and the Sink is able to accept it. Nack is asserted high, because during the previous clock cycle nothing has been received.

Clock cycle 4 After storing B, the destination's buffer is now full. The next coming flit cannot be stored before a new communication takes place between S and its downstream node. The Master will try to transfer the successive flit of the sequence, C, but will face the Stall signal controlled by the destination. In such a situation, M will keep the actual configuration until the Stall signal is unset. Concurrently, the received B flit is signaled as correct.

Clock cycle 5 When S has free space in its buffer memory, it will de-assert Stall signal and M will be able to complete the transfer of C.

Clock cycle 6 Master transfers the following flit, D. Let us suppose that something went wrong during the communication. Sink will store it, but the data received will be D', not a valid data word.

Clock cycle 7 After a redundancy check, the receiver signals to the transmitter that the previous flit transmission has been erroneous. In order to notify such event the Nack signal is asserted high. Since anyway any other flit following the corrupted one must be retransmitted, the current ongoing data flit, E, is discarded.

Clock cycle 8 The Sink module will be waiting for the transmitter to reply with the same flit signaled as corrupted. Nack signal will remain asserted high until a correct flit will be received. In the meanwhile, since a Nack signal has been received after a valid flit transmission, the transmitter will

take an arbitrary number of clock cycles in order to recover the flit that failed to be correctly transferred. Such number of clock cycles can even be 0, if the adopted policy is not to correct the flit at all but just to retransmit it. This depends on the degree of protection against transient faults. In fact, if the fault occurs on the link, a simple retransmission is enough. Vice versa, if the stored value in the switch buffer has been changed by a SEU, such change is irreversible and only correction can restore the original value, while retransmissions will result only into the same incorrect receipt of data. These are choices that the architecture designer has to take while implementing NACK/GO communication protocol in an actual network. The next valid transmission will be a reply to the error condition previously flagged.

Clock cycle 9 Now, the data that had been transmitted while the Nack signal was asserted high is transmitted again. D flit is signaled as correctly received.

Clock cycle 10 Finally, the last flit transmitted is acknowledged by the receiver.

#### 4.3 Novel Low-Power Fault-Tolerant Arbiter

By exploiting the retransmission capability provided by NACK/GO, we designed the fault-tolerant control path that supports NACK/GO flow control operation.

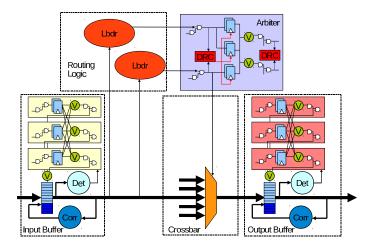

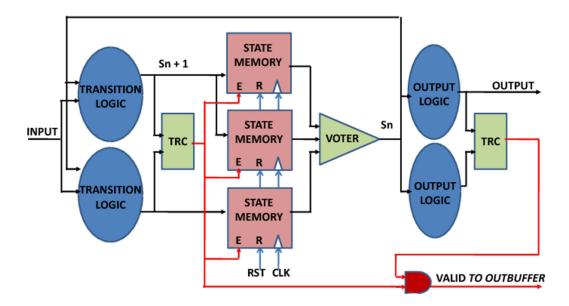

The novel fault-tolerant arbiter was designed following Figure 2.8. It represents an effective variant of a baseline TMR arbiter (like for the error correcting switch).

As showed in Figure 2.8, the transition logic, representing the arbiter combinational logic for computing the next FSM state, is doubled. Therefore, the outputs of the two transition logic instances are compared in a Two-Rail Checker (TRC) module (i.e. a redundant comparator block with fault tolerance capability) and feed the state memory register of the arbiter. The state memory register is triplicated as in a conventional TMR strategy although it is enabled by the TRC module output. When the two transition logic blocks generate the same result, then they are not affected by an error and the state memory register can sample the new state. On the other hand, the TRC block freezes the state of the arbiter registers when the transition

Figure 2.8: Fault tolerant arbiter implementation.

logic blocks provide different results. In this latter case, the valid signal to the output port is deasserted. As a consequence, the output port will not read the incoming information affected by errors, and since no valid data has been stored in the current clock cycle, the Nack signal will be asserted high in the following clock cycle. This will be interpreted by the input buffer as a request of retransmission.

Thus, the outputs of the three state memory registers are voted before feeding two instances of the output combinational logic with the arbiter current state. Then, the outputs of the combinational logic modules are compared in a TRC comparator following the previous implementation adopted for the transition logic modules. Finally, when the above mentioned comparator reveals an error, then the valid signal to the output port is deasserted and the information coming from the output combinational logic is discarded.

The baseline behavior of the arbiter remains the same: it selects between different inputs competing for the same output port, operating with a round robin arbitration policy in order to enforce fairness between all the requests. New conditions and events had to be managed in order to cope with error detection: whenever an error is detected in the output buffer, the Nack signal must be routed to the correct destination. If this takes place on the head flit of a packet, that stores the information about destination, in order to avoid

misrouting the current source will lose the grant acquired by the arbiter. In the following clock cycle, the route will be re-computed and the arbitration process will take place again. On the other hand, when an error is signaled for the last flit of a packet (tail flit), the sender has already lost the grant given by the arbiter and has no longer exclusive access to the output port. For this reason, the arbiter does not consider any new request, and the sender that had the grant in the previous clock cycle acquires again access to the output port. In this way the correct status of the various actors is re-established, and the corrected flit can now be retransmitted. Lastly, when a flit is signaled as corrupted while being transmitted (Trash signal asserted high), the arbiter must propagate this condition to the output port, and ignore the current transaction taking place. The trash signal is forwarded to the output buffer, that will ignore the current incoming flit.

#### 4.4 Fault-Tolerance of Routing logic and Buffer FSMs

In order to protect routing logic, two LBDR replicas directly feed the combinational logic cascaded to the TRC of the arbiter. A failure in the LBDR logic will be tackled by the arbiter's Two Rail Checkers, thus exploiting the cooperation with the arbiter to achieve fault-tolerance by means of an effective lightweight solution.

The status registers of buffer FSMs need additional protection. For this purpose, the simplest thing was to implement TMR in light of the low-complexity of replicated circuits. This solution is the same adopted for the error correction switch.

Figure 2.6 depicts the final NACK/GO switch architecture.

## 5 Integration with Network-Level Fault Tolerance

Although the above architectures have been primarily designed to tackle SEUs, they are both capable of handling intermittent faults.

Some physical effects such as wear-out end up in permanent faults, but are known to have a gradual onset. In practice, frequent transient faults affecting the same circuitry denote the possible onset of a permanent fault. Before this happens, the network routing function could be modified to exclude the affected circuit from communication traffic. NACK/GO lends itself to such a policy, since its retransmission and/or voting events may be notified to the global controller (e.g., via the dual bus in [27]) which may monitor the distribution and frequency of transient faults over time and eventually take the proper course of recovery action. Exactly the same policy can be supported by the error correcting switch by notifying correction and/or voting events to the controller.

## 6 Global Strategy for Self-Configuration

A distributed configuration strategy avoids single points of failure at the cost of significant resource over-provisioning. In fact, complex communication extensions are typically needed both for baseline operation of the configuration logic (additional signaling mechanisms with neighboring switches, complex routing computation or table update logic which may potentially render the switch multi-cycle, rule checking mechanisms for deadlock avoidance) and to improve the percentage of supported fault patterns (e.g., broadcasting, virtual channels, hardware timeouts, large storage or combinations thereof). The main reason lies in the lack of visibility of global network state at a NoC switch. Therefore, this latter has to take the proper course of action to become aware of the state of neighboring nodes, to find a routing path to every network destination and to avoid deadlock and livelock. This is a lengthy process that partially offsets the benefits of distributed configuration. Even accepting this, final routing solutions cannot be always guaranteed to be completely deadlock-free and frequently incur mis-routing [2].

The suitability of these requirements for the embedded computing domain is questionable. Therefore, the investment of our work is on a centralized approach, which envisions a global controller with full visibility of the network state and that is able to reprogram the routing mechanism of the switches accordingly.

The previous section has already showed that minimizing signaling needs from the network to the controller and vice versa is an orthogonal concern across all layers of the reconfiguration framework, starting from the routing mechanism up to the optimized design of the signaling architecture.

Above all, the main challenge we tackle in this thesis is to carry vital diagnosis and configuration information from the network to the controller and vice versa in a reliable way, since manufacturing yield is tightly related to the reliability of these communications. If we use the data network for such a critical information exchange, the intricacy is again associated with the reduced view each switch has of the network failure pattern, which tends to overprovision the NoC architecture (e.g., virtual channels, flooding capability) or to uncover many failure combinations. Alternatively, the controller might discover by itself the failure pattern by means of a lengthy and non-trivial process starting from neighboring nodes and through them reaching the most remote nodes. Finally, enforcing fault-tolerance of the whole data network for the sake of safe configuration is overly expensive area- and performance-wise, even when more advanced techniques than NMR (N-modular redundancy) are used [21].

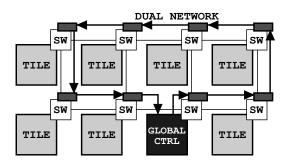

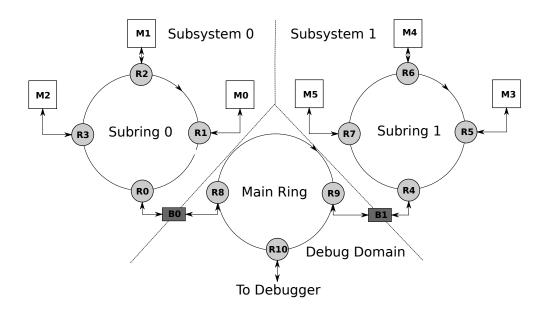

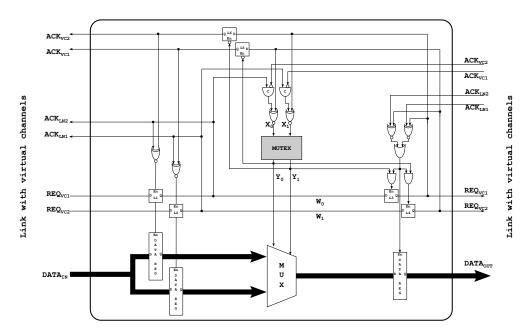

The above reasons justify the use of a dedicated dual-network for control signaling. The network is composed by a set of replicated routing primitives, each one associated with, and connected to, a switch of the main data NoC. Unlike the full featured and richly connected main NoC, the dual NoC implements a straightforward ring topology where the routing primitives are simply cascaded. The global controller closes the ring, as illustrated in Fig.2.9.

Figure 2.9: Topology of the dual network.

Overall, the dual network has to carry 10 diagnosis bits to the controller from every switch, and to get back 26 routing configuration bits to them. These relatively small requirements leave ample room for designing the dual network aggressively for fault tolerance while marginally impacting overall NoC area footprint (see section 7).

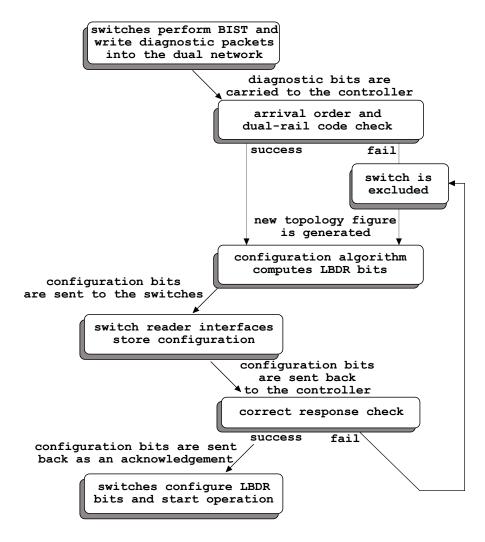

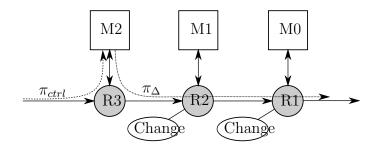

The operating principle of our configuration strategy is as follows (see Fig.2.10): at system bootstrap, after performing the BIST/BISD phase, each switch has to communicate the result of its diagnosis to the global controller through the dual network. However, in order to make sure that no transfer errors occurred during this communication (unmasked by the fault-tolerance mechanism), a specific online testing protocol is implemented <sup>1</sup>.

Figure 2.10: Configuration strategy at glance.

In particular, the writer interface of each switch (into its associated routing

<sup>&</sup>lt;sup>1</sup>The word "online" here is relative to the configuration process.

primitive) sends the diagnostic bits by leveraging a two-rail encoding scheme in time. This way, the global controller can check whether an unmasked fault has corrupted the diagnosis information of a specific switch. In case, the switch is considered to be unusable and left out of the configuration process. Also, the arrival order of diagnostic bits is deterministic, therefore the controller can easily realize whether a switch is so corrupted not to be able to transmit. At the end of this initial signaling phase, the new topology connectivity pattern is derived, since diagnosis bits indicate which links/switch ports are faulty. Therefore, a configuration algorithm can be executed, thus computing configuration bits for the LBDR logic of each switch. These bits are then sent to all the switches via the dual network. Based on our testing protocol, switches send back the received bits to the controller, so that this latter can check whether the transmission was successful. If transmitted and received data match, then the controller sends them again to the switches as an acknowledgment. Upon the arrival of the same configuration bits twice, the switches then configure LBDR bits and trigger switch operation. This is done by deactivating the flow control stall signal to neighboring switches, which prevents to store incoming data until the configuration phase completes. This is the same signal used for normal flow control in the main NoC at regime.

The rationale behind the three-way handshake protocol is that, the *reader* interface of the switch from the routing primitive needs to be tested as well in order to make sure that it is able to correctly receive data and reconfigure the routing mechanism accordingly.

Now, let us assume that the controller detects that a switch is not able to correctly receive configuration bits. Then, the switch is excluded and the configuration algorithm recomputes routing, connectivity and deroute bits selectively for the neighboring switches, thus accounting for the new change of the actual topology. Other switches are not involved in this signaling round and are kept temporarily blocked. Affected switches in turn receive a different set of configuration bits than before, therefore they send them back again to the controller to check correct receipt. The procedure is iterated until no mismatch is detected by the controller: at that time, the acknowledgment is sent to all switches, so that they start operation concurrently.

Please note that unmasked stuck-at faults in the dual network are not necessarily incompatible with its correct operation. In fact, should they match by chance the configuration bit transmitted on that bit, the configuration works correctly. Every time the configuration bits are changed, they might reveal the stuck-at bit, but in this case the three-way handshake enables to detect this at the controller and to conservatively discard the affected switch.

Our configuration strategy aims at correctly configuring switches of the main NoC even in the presence of faults in the dual network and prefers to discard those switches that cannot either send diagnostic bits or receive configuration bits correctly because of unmasked faults by the fault-tolerance mechanisms. We want to avoid flagging a switch or a link as operational when it is actually not working, since this would make network operation not trustworthy. We rather prefer to conservatively discard well-behaving components when their ability to correctly interact with the controller is uncertain. Next section will detail the architecture of the routing primitive.

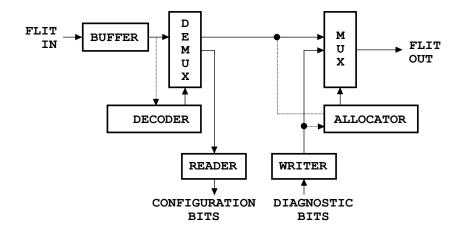

## 7 Routing Primitive Architecture

From an architecture viewpoint (see Fig.2.11), the routing primitive resembles an oversimplified version of an input buffered clocked switch. An input decoder discriminates between packets destined to the controller (collision between these latter and packets originating from the local switch is solved by an allocator) and those destined to the local switch. All packets on the dual network have a fixed 3 flit length. Flit width is 15 bits. The input buffer has 2 slots (for stall/go flow control management) while the allocator implements a fixed priority algorithm in light of the operating principle of the dual network. This latter is as follows. After the BIST phase completes in the local switch, diagnostic bits are generated and forwarded to the routing primitive through the writer interface. Packets are 3 flits long. The header flit carries sender switch ID. The second flit carries diagnostic bits while the third one carries negated diagnostic bits. The controller transmits configuration bits again in 3 flits. The header contains target switch ID and flit type. The second and third flits contain LBDR bits. Whenever the primitive receives a configuration packet, the reader interface eliminates the header information

Figure 2.11: Dual network routing primitive.

and extracts the LBDR bits.

The dual network is a critical component for the correct configuration of the system. Therefore, we decided to provide fault-tolerance capability to it by means of triple modular redundancy (TMR). This latter has been preferred to information redundancy (e.g., error correcting codes, ECCs) for ease of design. In fact, TMR only requires the replication of the routing primitive in the dual network, whereas the use of ECCs (such as Hamming codes), although requiring less overhead, would imply the utilization of ad-hoc design techniques to avoid that signal fan-outs introduce errors that cannot be corrected.

Figure 2.12: TMR approach with per primitive voting system.

The simplest approach to TMR implementation consists of replicating the dual-network three times and to vote it at the input of the controller interface (for switch-to-controller signaling). This approach, however, has a probability of failure that does not scale well with the size of the network. In this regards, let  $p_f$  be the probability that, because of faults, a single routing primitive is unable to deliver one input flit to the target output port uncorrupted. When TMR is applied with voting at the controller, the probability  $P_i$  that the i-th stage of the replicated dual network fails to correctly communicate with the controller is:

$$P_i = 1 - \text{Prob}\{\text{at least two voter inputs are correct}\} = 1 - \left(\binom{3}{2}\left((1 - p_f)^i\right)^2\left(1 - (1 - p_f)^i\right) + \left((1 - p_f)^i\right)^3\right)$$

(2.1)

where  $(1-p_f)^i$  denotes the probability that a voter input correctly receives the input of the *i*-th stage. In case  $p_f \ll 1$ , the above equation provides  $P_i \simeq 6i^2p_f^2$ . Of course, the presence of the term  $i^2$  gives rise to problems in the presence of large values of *i* (the furthest away nodes from the controller). Also, since our dual network is not a one-way chain but a ring where configuration bits also flow,  $P_N$  (where N is the number of ring nodes) coincides with the failure probability of the ring as a whole. To solve this problem we decided to vote at the output of each stage of the dual network (see Fig. 2.12). In this scheme, in fact,  $P_i$  scales in a better way because it depends on *i*. In particular, let  $q_f$  be the probability that a routing primitive of the dual network or its output voter are faulty (therefore,  $q_f > p_f$  because of the additional voter area). Therefore, the probability  $P_b$  that a triplicated primitive and associated output voters work is:

$$P_b = \text{Prob}\{\text{at least two voters outputs are correct}\} = \left(\binom{3}{2}(1-q_f)^2(1-(1-q_f)) + (1-q_f)^3\right) \quad (2.2)$$

Finally, the probability that the *i*-th stage of the fault-tolerant dual network does not communicate with the controller is:

$$P_i = 1 - P_b^i \tag{2.3}$$

that if  $q_f \ll 1$  becomes  $P_i \simeq 3iq_f^2$ , thus showing a linear dependency on i that scales better with the size of the dual network. Therefore, the scheme in Fig. 2.12 is adopted. It should be noted that also flow control signals (valid and stall/go) are voted. From the figure, voting of the incoming configuration bits is also apparent. Should a fault affect this voter, the online testing procedure is able to detect this, since transmitted configuration bits by the controller would not match the same bits that the switch sends back to the controller for a double check, and the switch would be discarded.

## 8 Experimental Results

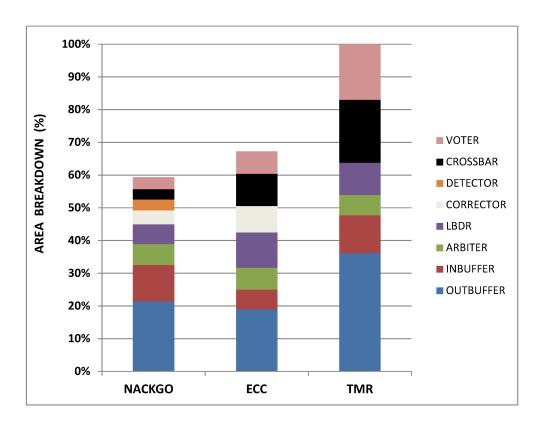

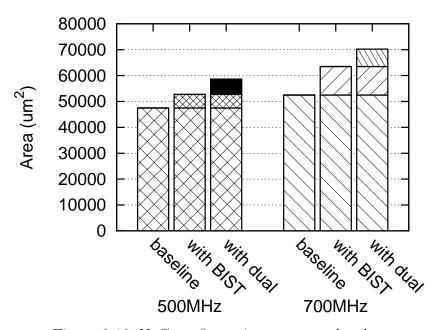

Figure 2.13: Area comparison between TMR, ECC and NACK/GO switch.

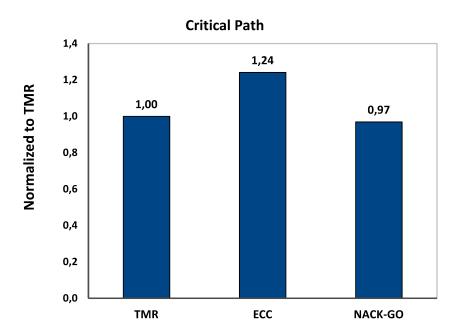

Figure 2.14: Critical path comparison between TMR, ECC and NACK/GO switch.

#### Area and Critical Path of the Fault-Tolerant Switch 8.1 Architectures

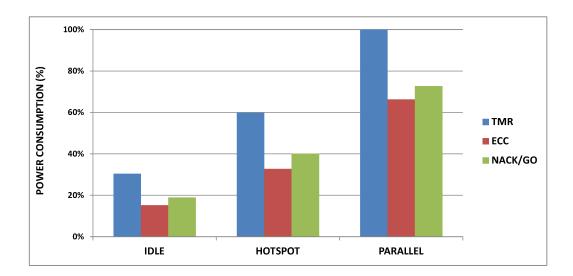

In this section we illustrate the experimental results carried out for the three switches (TMR, NACK/GO, ECC) in terms of area, critical path and power consumption. All the analyzes discussed in this work have been carried out by means of a backend synthesis flow leveraging mainstream industrial tools. The technology library is a low-power low-Vth 65nm STMicroelectronics library.

The area results are showed in Figure 2.13, while critical path comparison is presented in Figure 2.14. Please note that all the results are normalized with respect to the plain TMR solution.

The area of the TMR switch is not only given by the various triplicated modules, but a non-negligible contribution comes from the numerous voters, instantiated not only in the control path inside the switch, but also for every bit of the data path of every input channel. In addition, due to the large area footprint, long wires affect performance of the component. Numerous electric buffers are instantiated during place&route to speed up transmission

on internal paths, leading to additional area overhead. The result is a total area that is much more than triplicated (around 4.5x) with respect to the baseline solution, and a performance drop that exceeds the pure contribution of the voters on the critical path. These are very interesting second order effects that are typically overlooked in most literature surveys.

The version of the switch correcting at every clock cycle (ECC) greatly reduces the area footprint with respect to TMR, while almost balancing the area figures of the NACK-GO switch. Unfortunately, the corrector modules lie on the critical path and operate at every clock cycle, and not only upon fault detection as in the NACK-GO switch, so the performance is negatively affected. The critical path is 27% longer than the NACK-GO switch. The presented results refer to a single cycle switch. Please note that pipelining the correction phase would only speed up the throughput, but would negatively affect the latency making the switch multi-cycle. Furthermore it is important to note that this solution does not guarantee complete fault tolerance, because correctors are not immune against transient faults which may result in packet misrouting.

As far as the NACK/GO switch is concerned, a non-negligible area contribution comes from detector and corrector modules. These count for almost 13% of the total area. In many works in the literature targeting transient faults the problem of data corruption inside buffers is typically omitted, therefore the overhead of correctors in retransmission-oriented solutions is not accounted for.

When comparing NACK-GO with the ECC strategy, we can notice a similar area footprint for the output buffers while the ECC solution presents a lighter input buffer. This latter result is due to the oversizing of the NACK-GO input buffer. Indeed, a higher amount of slot buffers is required by NACK-GO with respect to STALL/GO. As regards the correctors, they bring a high area overhead to the ECC solution since they lie on the switch critical path. On the other hand, the NACK-GO switch has smaller correctors but it requires detectors not adopted by the ECC counterpart. As a consequence, the two switches require a similar total amount of area for correction and detection modules. Concerning the control path, the novel arbiter proposed in section 4.3 does not directly bring area benefit. In fact, the complexity